#

К. ФРИКЕ

Вводный курс цифровой электроники

Перевод с немецкого под редакцией и с дополнением В.Я. Кремлева

Рекомендовано Московским Институтом Электронной Техники (МИЭТ) в качестве учебного пособия для студентов, специализирующихся в области проектирования цифровых интегральных схем

ТЕХНОСФЕРА Москва 2003 К.Фрике

Вводный курс цифровой электроники

Москва:

Техносфера, 2003. - 432c. ISBN 5-94836-015-6

Книга дает научно обоснованное введение в цифровую технику, предоставляя в полной мере ее основы, вплоть до конструирования и программирования. Читатель получает знания, которые делают возможным понимание большинства цифровых технических схем.

Особенно детально рассматривается синтез логических схем. На примерах обсуждаются наиболее часто применяемые стандартные схемы — мультиплексоры и преобразователи кода. Подробно анализируются основы арифметики с фиксированной запятой и аппаратная реализация арифметических блоков.

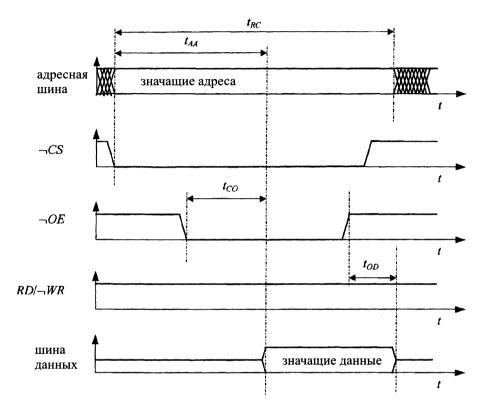

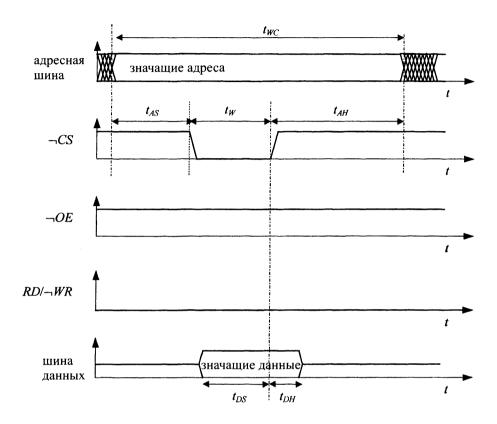

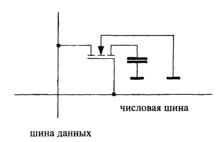

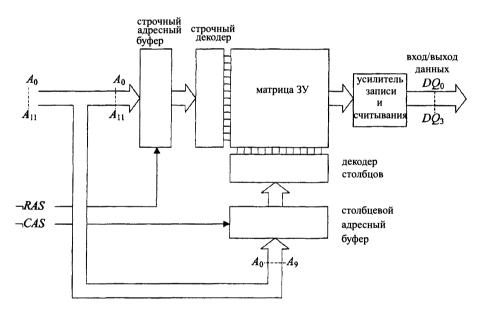

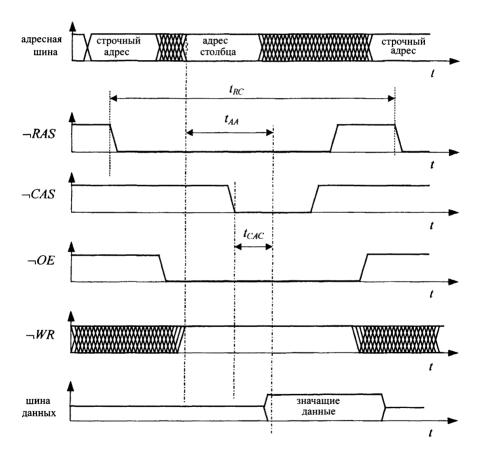

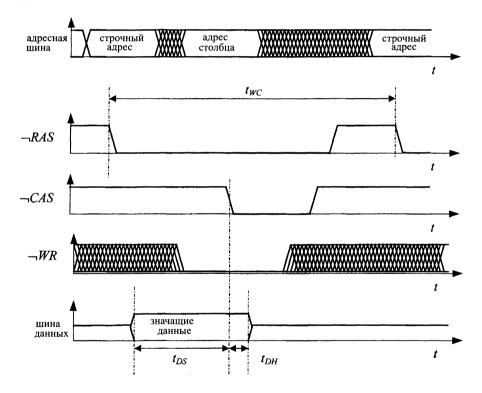

Для различных блоков ЗУ приводятся типовые временные диаграммы.

В качестве введения в проектирование структур компьютеров представлены драйверы с программным управлением.

Подробно описана элементная база цифровых устройств и рассмотрены ключевые проблемы их энергетики. Дано четкое введение в микропроцессорную технику.

Учебное пособие будет полезно инженерам-практикам, активно использующим элементную базу цифровой техники, программирование микроконтроллеров и ПЛИС.

© 2001 Friedr. Vieweg & Sohn Verlagsgesellschaft mbH, Braunschweig/Wiesbaden Der Verlag Vieweg ist ein Unternehmen der Fachverlagsgruppe Bertelsmann Springer © 2003, ЗАО «РИЦ «Техносфера» перевод на русский язык, оригинал-макет, оформление

ISBN 5-94836-015-6 ISBN 3-528-13861-0 (Hem.)

#### Содержание

| 1 лава<br>Введ |                                                        | 16         |

|----------------|--------------------------------------------------------|------------|

| Глава          | a 2.                                                   |            |

| Коди           | рование и системы счисления                            | 19         |

| 2.1.           |                                                        | 19         |

| 2.2.           |                                                        | 20         |

| 2.3.           | Арифметические операции с фиксированной запятой в      |            |

|                |                                                        | 22         |

| 2.3            |                                                        | 22         |

| 2.3            | 1 1                                                    | 23         |

| 2.3            |                                                        | 23         |

| 2.3            | 1 (1)                                                  |            |

|                | (точное дополнение, two's complement)                  | 24         |

| 2.3            | 1 1 11                                                 |            |

|                | дополнения                                             | 25         |

| 2.3            | .6. Переполнение числового диапазона                   | 26         |

| 2.3            | .7. Умножение                                          | 27         |

| 2.3            | .8. Деление                                            | 28         |

| 2.4.           | Шестнадцатеричный код                                  | <b>29</b>  |

| 2.5.           | Восьмеричный код                                       | <b>3</b> 0 |

| 2.6.           | Код Грея                                               | <b>3</b> 0 |

| 2.7.           | Двоично-десятичный код                                 | 31         |

| 2.8.           | Алфавитно-цифровые коды                                | <b>32</b>  |

| 2.9.           | Упражнения                                             | <b>32</b>  |

| Глава          | a <b>3.</b>                                            |            |

| Пере           | еключательная алгебра                                  | 34         |

| 3.1.           | Переключательная переменная и переключательная         |            |

|                | функция                                                | 34         |

| 3.2.           | Двухразрядные переключательные функции                 | 36         |

| 3.3.           | Вычислительные правила                                 | 38         |

| 3.4.           | Каноническая дизъюнктивная нормальная форма            |            |

|                | (KDNF)                                                 | 40         |

| 3.5.           | <br>Каноническая конъюнктивная нормальная форма (KKNF) | 41         |

| 3.6.           | Представление функций с помощью KKNF и KDNF            | 42         |

| 3.7.           | Минимизация с помощью переключательной алгебры         | 44         |

|                |                                                        |            |

|   | ₹.   |

|---|------|

|   | 1111 |

| E | m    |

| ) | ]]]  |

| _ | //// |

| _ | "    |

| 3.8.        | Способ упрощенной записи                             | 45  |

|-------------|------------------------------------------------------|-----|

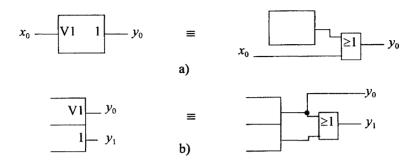

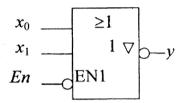

| 3.9.        | Символическое обозначение логических элементов       | 46  |

| 3.9         | 0.1. Основы структуры символов                       | 46  |

| 3.9         | 0.2. Индексация зависимости                          | 47  |

| 3.9         | о.3. Зависимость вида И (G)                          | 47  |

| 3.9         | 0.4. Зависимость по типу ИЛИ (V)                     | 48  |

| 3.9         | 0.5. Зависимость по типу EXOR (N)                    | 49  |

| 3.9         | 0.6. Образующая соединение зависимость (Z)           | 49  |

| 3.9         | 0.7. Зависимость с передачей (X)                     | 49  |

| 3.10.       | Упражнения                                           | 50  |

| Глав        | a 4.                                                 |     |

| Пове        | едение логических вентилей                           | 52  |

| 4.1.        | Положительная и отрицательная логика                 | 53  |

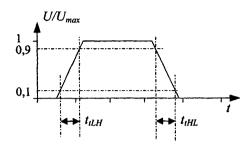

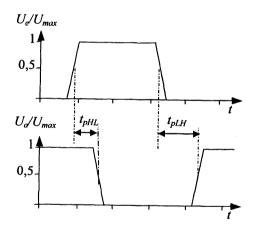

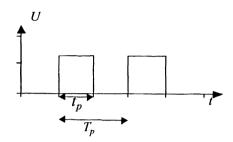

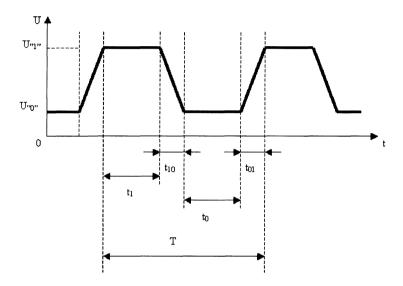

| 4.2.        | Определение времени переключения                     | 54  |

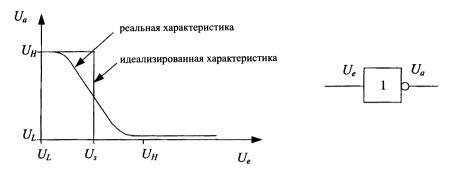

| 4.3.        | Передаточная характеристика, запас по помехоустойчи- |     |

|             | вости                                                | 56  |

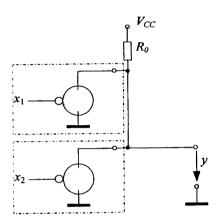

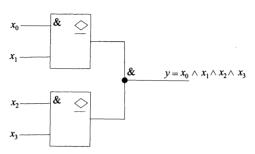

| 4.4.        | Вентили                                              | 58  |

| 4.4         | 1.1. Вентили с открытым коллектором (open collector) | 60  |

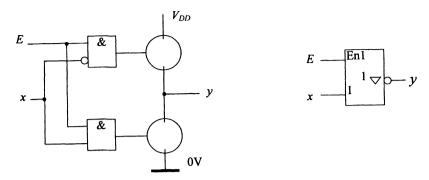

| 4.4         | 1.2. Вентиль с тремя состояниями                     | 61  |

| 4.5.        | Упражнения                                           | 62  |

| Глав        | a 5.                                                 |     |

|             | иотехника                                            | 64  |

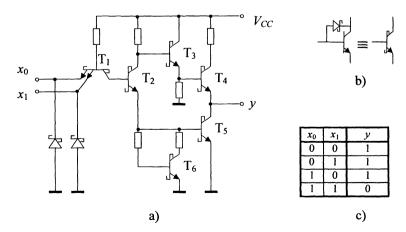

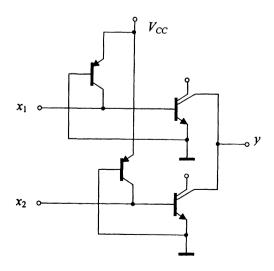

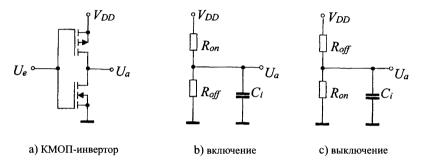

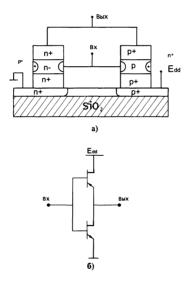

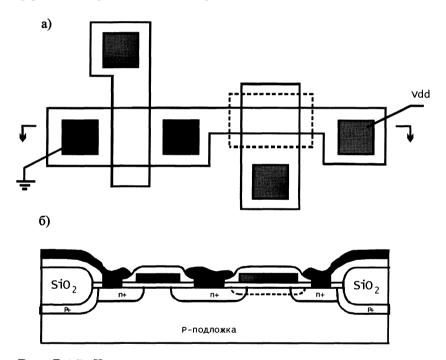

| 5.1.        | КМОП                                                 | 64  |

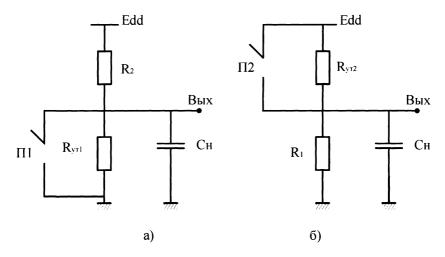

| •           | .1. Нагрузочная способность                          | 66  |

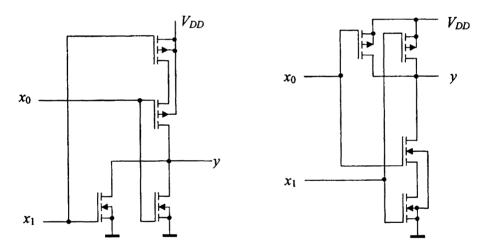

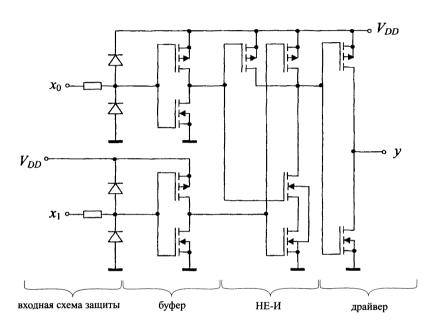

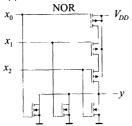

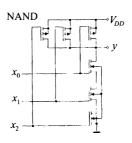

|             | .2. Основные схемы NAND и NOR                        | 67  |

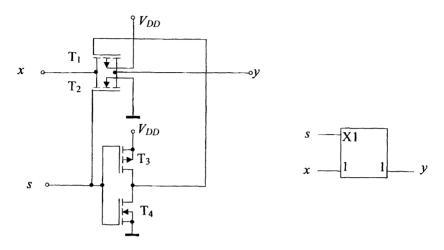

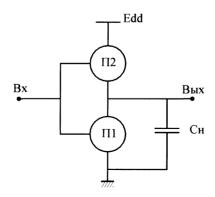

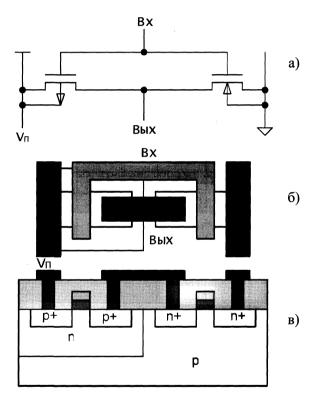

|             | .3. Передаточный вентиль                             | 68  |

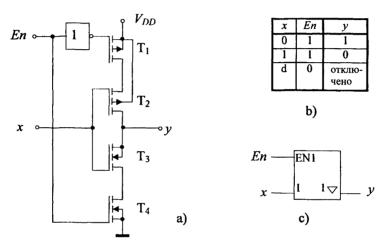

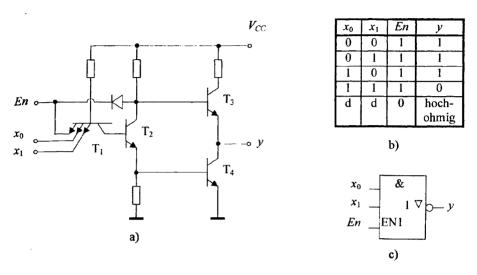

|             | .4. Элемент с тремя состояниями                      | 69  |

|             | .5. Специфические свойства КМОП                      | 69  |

| 5.2.        | ТТЛ                                                  | 71  |

| 5.2         |                                                      | 72  |

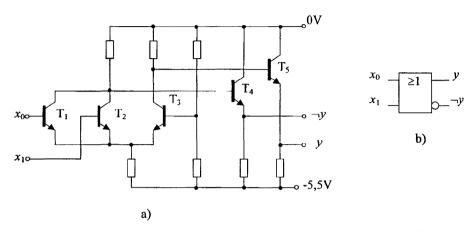

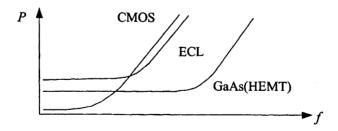

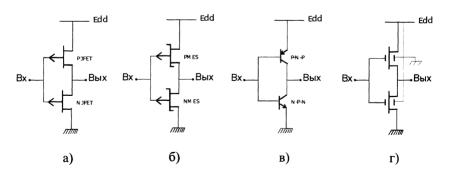

| 5.3.        | Эмиттерно-связанная логика                           | 73  |

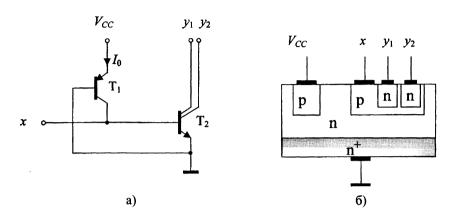

| 5.4.        | Интегральная инжекционная логика (I <sup>2</sup> L)  | 74  |

| 5.5.        | Рассеиваемая мощность и характеристики переключе-    | • - |

|             | ния транзисторных переключателей                     | 76  |

| 5.6.        | Упражнения                                           | 78  |

| Допо        | олнение.                                             |     |

|             | ентная база цифровых устройств. Энергетика обработки |     |

|             | овой информации                                      | 79  |

| Д.1.        | Введение                                             | 79  |

| <del></del> | 220401110                                            |     |

| Д.2. Э | нергетика и скорость производства цифровой инфор-  |     |

|--------|----------------------------------------------------|-----|

| M      | ации                                               | 79  |

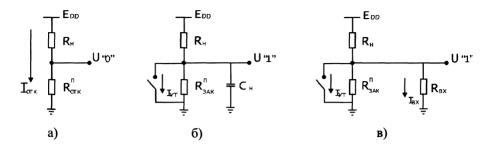

| Д.2.1  | . Классификация вентилей как энергопотребителей    | 81  |

| Д.2.2  | 2. Общие вопросы энергетики цифровых вентилей      | 84  |

| Д.2.3  | . Скорость производства информации                 | 93  |

| Д.3. С | рганизация и энергетика цифровых схем              |     |

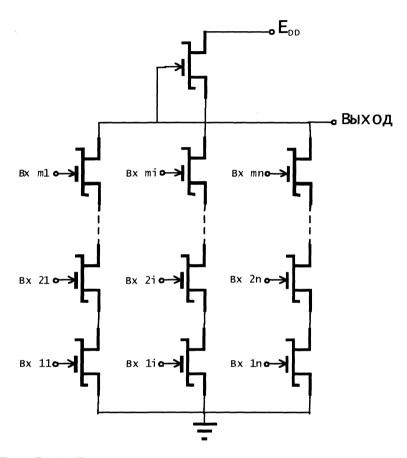

| б      | ез отношения                                       | 105 |

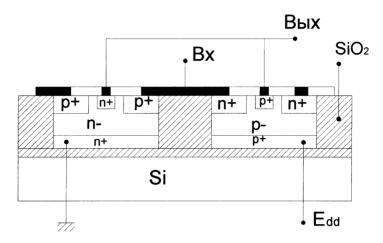

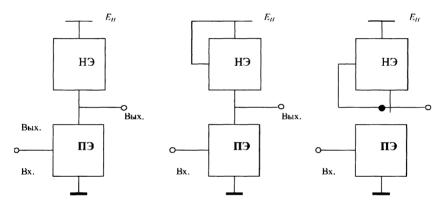

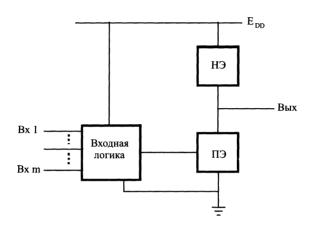

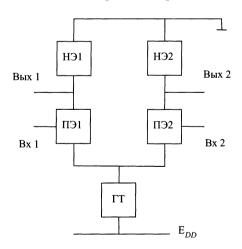

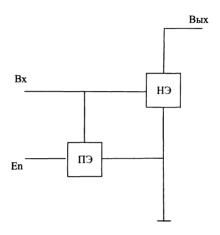

| Д.3.1  | . Общий принцип организации схем и схемотехниче-   |     |

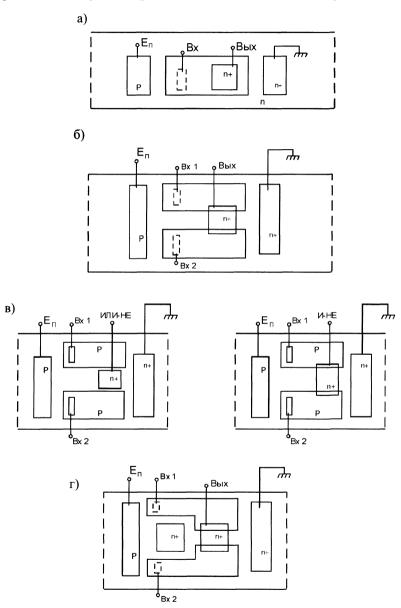

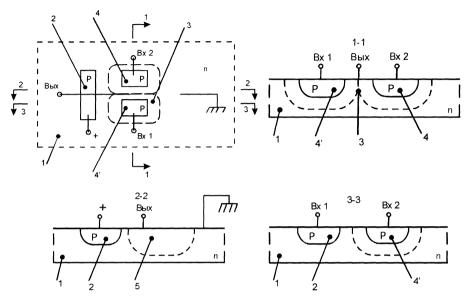

|        | ские разновидности                                 | 106 |

| Д.3.2  | . Энергетика производства информации               | 114 |

| Д.3.3  | . Мощностные характеристики                        | 116 |

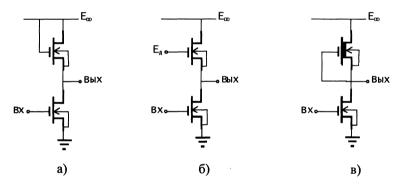

| Д.4. С | хемотехнические и энергетические характеристики    |     |

| Л      | огических схем с отношением                        | 118 |

| Д.4.1  | •                                                  | 119 |

| Д.4.2  | . Основные схемотехнические и структурно-тополо-   |     |

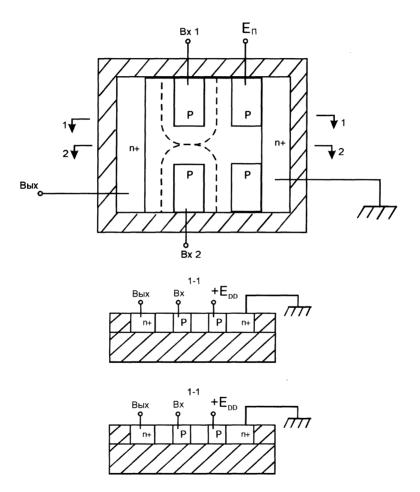

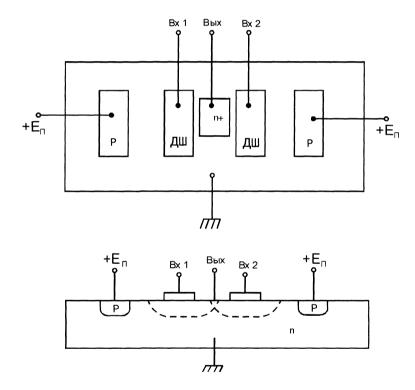

|        | гические типы                                      | 121 |

| Д.4.3  | . Особенности обработки информации и энергопотре-  |     |

|        | бления                                             | 128 |

| Д.4.4  | . Особенности энергопотребления                    | 130 |

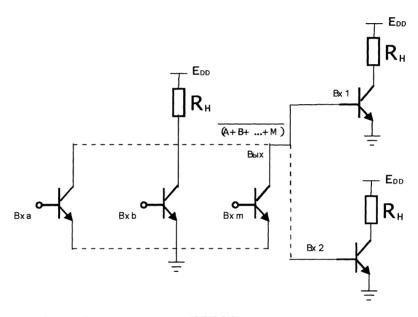

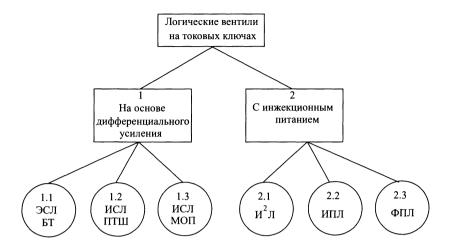

| Д.5. С | хемотехника логических вентилей на токовых ключах  | 132 |

| Д.5.1  | . Общий принцип схемотехнической организации и     |     |

|        | классификация                                      | 133 |

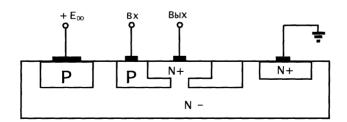

| Д.5.2  | . Интегральная инжекционная логика                 | 136 |

| Д.5.3  | . Быстродействие и энергетика токовых ключей       | 145 |

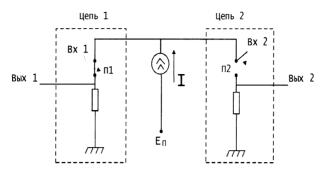

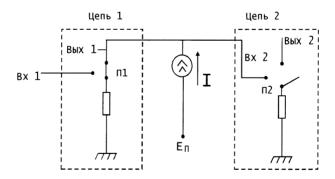

| Д.6. П | ринципы организации частично диссипативных схем    | 149 |

| Д.6.1  | • • • • • • • • • • • • • • • • • • • •            | 150 |

| Д.6.2  | _ ·                                                |     |

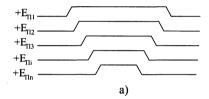

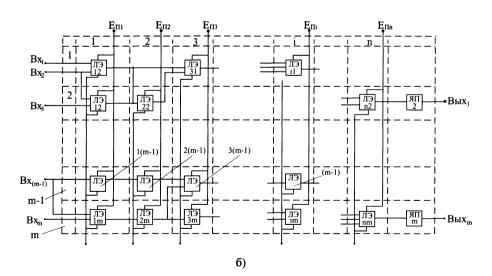

|        | пульсным питанием                                  | 153 |

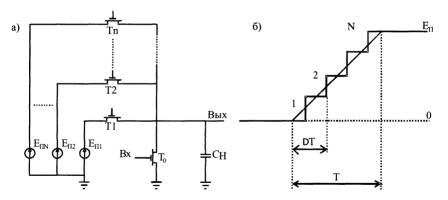

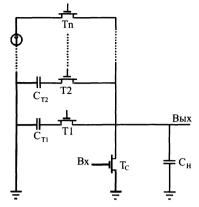

| Д.6.3  | . Вентили со ступенчатой перезарядкой выходной ем- |     |

|        | кости                                              | 157 |

| Д.7. В | ентили с нетрадиционной организацией энергопитания | 161 |

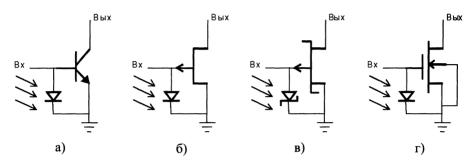

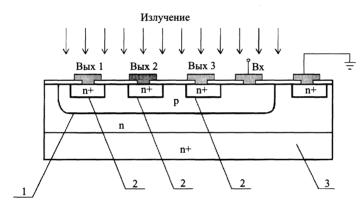

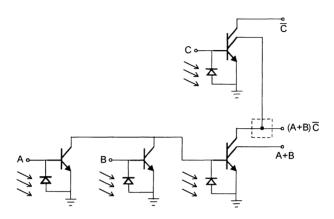

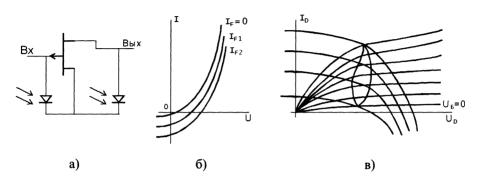

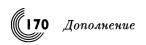

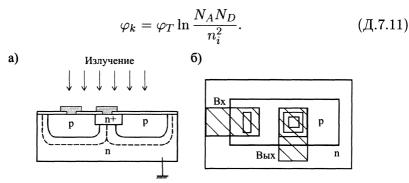

| Д.7.1  | . Питание ионизирующим излучением                  | 161 |

| Д.7.2  |                                                    |     |

|        | шения базовых логических вентилей, питающихся      |     |

|        | излучением                                         |     |

| Д.8. З | аключение                                          | 172 |

| Глава  | 6.                                                 |     |

| Логич  | еские схемы                                        | 173 |

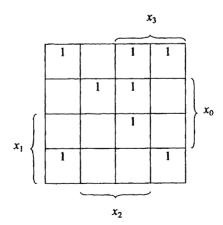

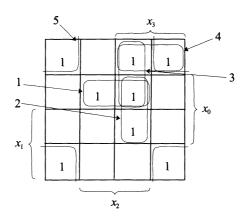

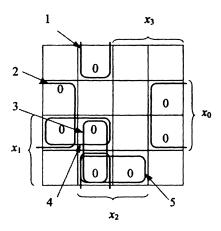

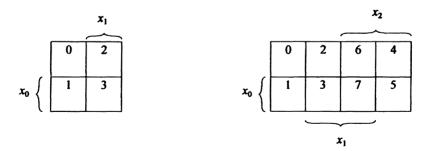

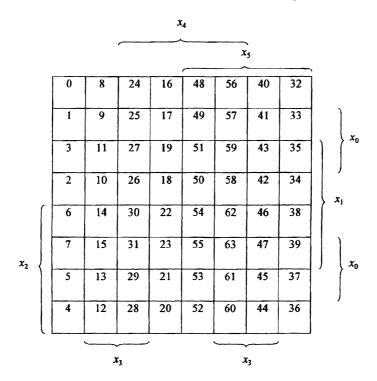

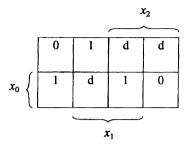

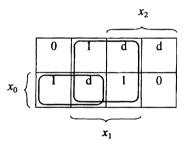

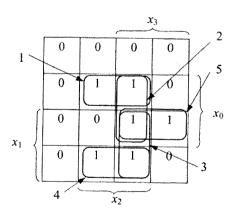

| 6.1. M | Іинимизация с помощью диаграмм Карно-Вейча         | 173 |

| 6.1.1. |                                                    |     |

| 6.1.2.   | Минимизация нормальной KKNF                          | 177 |

|----------|------------------------------------------------------|-----|

| 6.1.3.   | Диаграммы Карно-Вейча для 2, 3, 4, 5, 6 входных      |     |

|          | переменных                                           | 178 |

| 6.1.4.   | Неполностью заданные функции                         | 178 |

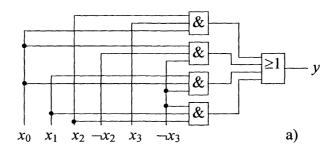

| 6.2. Спо | особ Квина-Мак-Класки                                | 180 |

| 6.3. Дру | угие направления оптимизации                         | 184 |

| 6.3.1.   | Преобразование логической схемы И/ИЛИ в схему НЕ-И . | 185 |

| 6.3.2.   | Преобразование логической схемы ИЛИ/И в логи-        |     |

|          | ческую схему НЕ-ИЛИ                                  | 186 |

| 6.4. Bos | действие времени задержки на логические схемы        | 187 |

| 6.4.1.   | Отрицательное воздействие на структуру               | 187 |

| 6.4.2.   | Отрицательное воздействие на функционирование        | 189 |

| 6.4.3.   | Классификация отрицательных воздействий              | 190 |

| 6.5. Упр | мнения                                               | 190 |

| Глава 7. |                                                      |     |

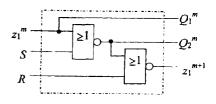

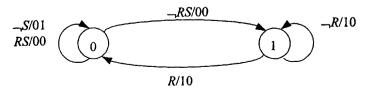

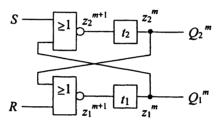

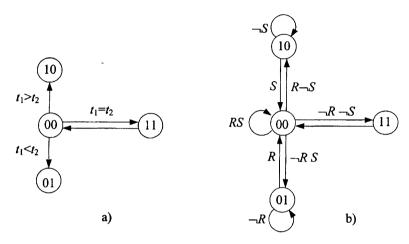

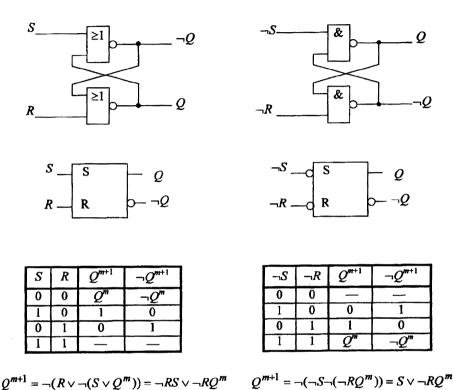

| Асинхро  | онные триггеры                                       | 193 |

| 7.1. При | инципиальные особенности структуры триггеров         | 194 |

| -        | ылиз асинхронных триггеров                           |     |

|          | тематический анализ                                  |     |

|          | ьлиз с учетом задержки вентилей                      |     |

|          | менты ЗУ                                             |     |

| 7.5.1.   | <b>RS</b> -триггер                                   | 201 |

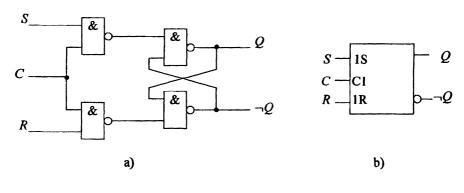

| 7.5.2.   | <b>RS</b> -триггер с тактовым входом                 | 201 |

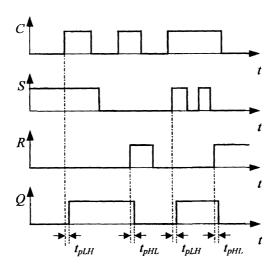

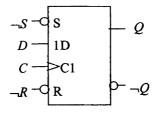

| 7.5.3.   | <b>D</b> -триггер                                    | 204 |

| 7.5.4.   | D-триггер с управлением по переднему фронту им-      |     |

|          | пульса                                               | 205 |

| 7.5.5.   | Управление передним и задним фронтом                 | 210 |

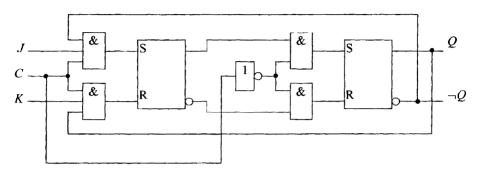

| 7.5.6.   | J-K-триггер                                          | 211 |

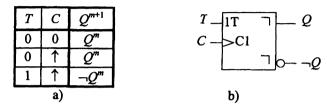

| 7.5.7.   | Т-триггер                                            | 212 |

| 7.5.8.   | Пример                                               | 213 |

| 7.5.9.   | Общее о триггерах                                    | 213 |

| 7.6. Упр | ажнения                                              | 216 |

| Глава 8. |                                                      |     |

| Синхрон  | ные драйверы                                         | 219 |

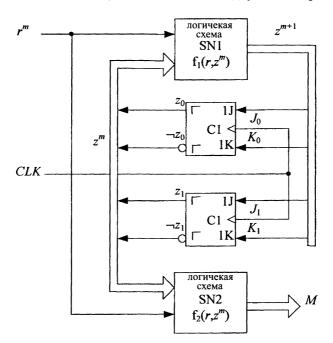

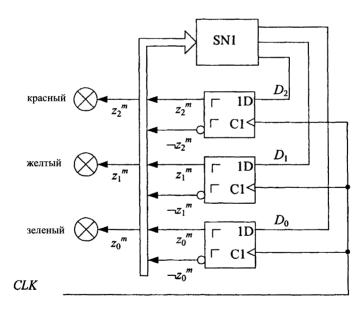

| 8.1. Син | итез драйверов (пример 1)                            | 219 |

| 8.1.1.   | Постановка задачи                                    |     |

| 8.1.2.   | Формирование диаграммы состояний                     |     |

| 8.1.3.   | Структура схемы управления электромеханически-       |     |

|          |                                                      | 221 |

| 8.1.4.   | Формирование таблицы последовательности состояний    |     |

|          |                                                      |     |

| 8.1.5.          | Формирование таблицы запуска и таблицы выход-    |      |

|-----------------|--------------------------------------------------|------|

|                 | ных сигналов                                     | 222  |

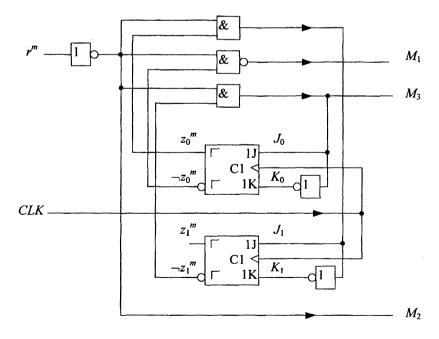

| 8.2. Син        | тез драйверов (пример 2)                         | 225  |

| 8.2.1.          | Постановка задачи                                |      |

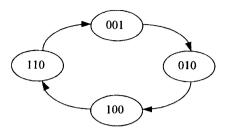

| 8.2.2.          | Составление диаграммы состояний                  | 225  |

| 8.2.3.          | Составление таблицы последовательности состояний |      |

| 8.2.4.          | Разработка логической схемы для запускающих      |      |

|                 | сигналов                                         |      |

| 8.2.5.          | Полная таблица состояний                         | 227  |

| 8.2.6.          | Полная диаграмма состояний                       | 228  |

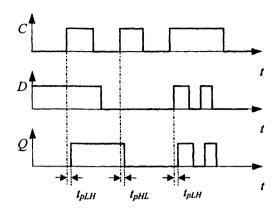

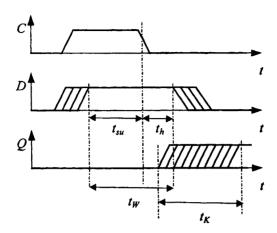

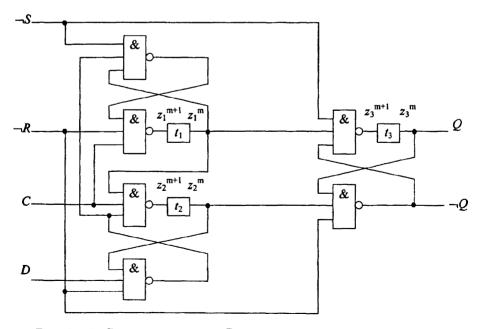

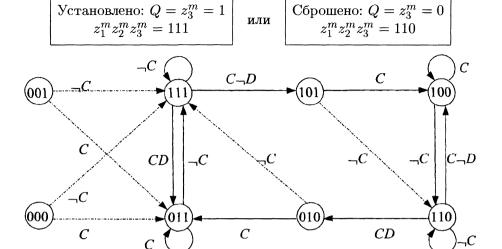

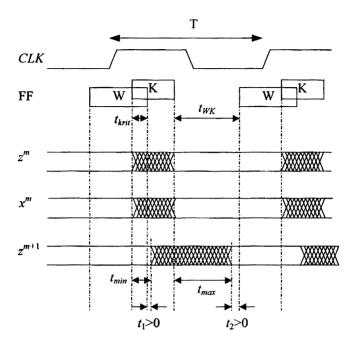

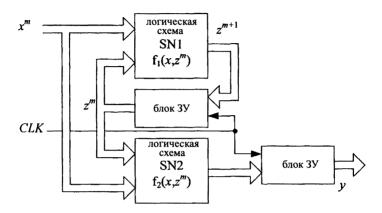

| 8.2.7.          | Временные характеристики драйверов               | 229  |

| 8.3. Упр        | ажнения                                          | 231  |

| Глава 9.        |                                                  |      |

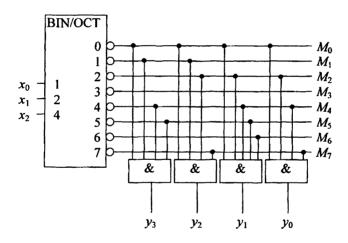

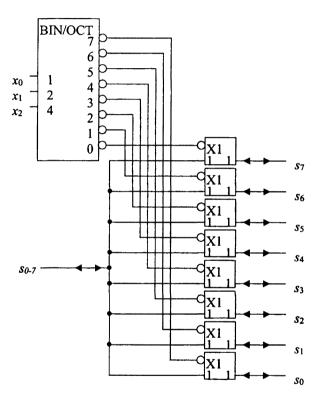

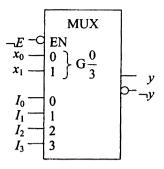

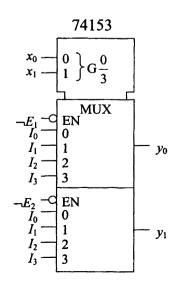

| Мульти          | плексоры и преобразователи кода                  | 234  |

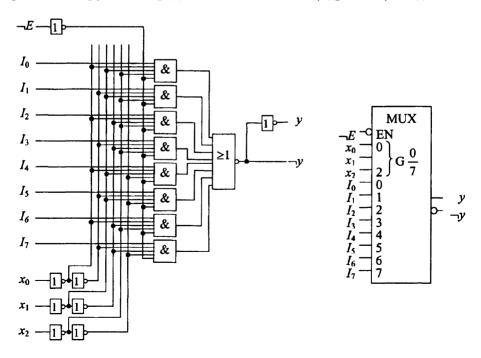

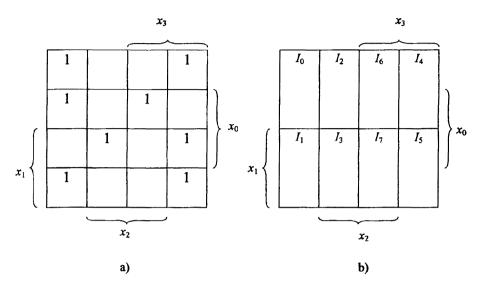

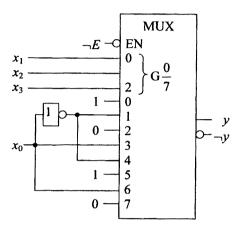

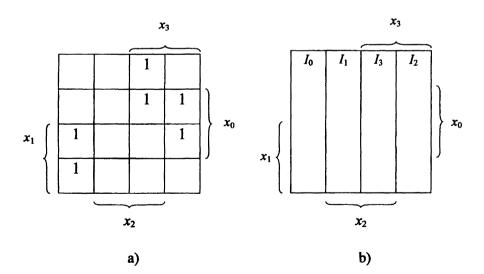

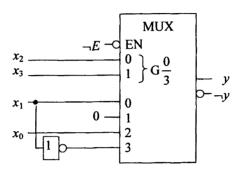

| 9.1. MyJ        |                                                  | 234  |

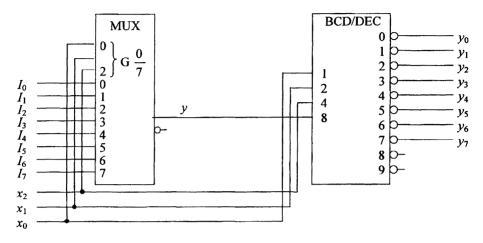

| •               | Реализация функций мультиплексора                |      |

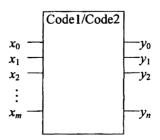

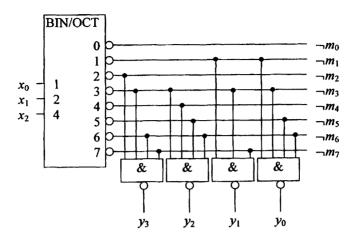

|                 | образователь кода                                |      |

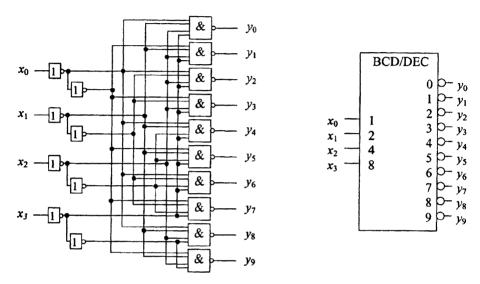

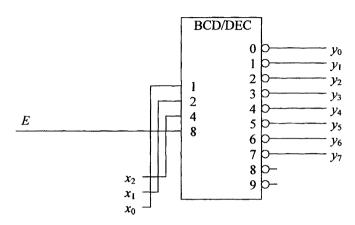

| 9.2.1.          | Преобразователь двоично-десятичного кода в деся- |      |

|                 | тичный код 7442                                  | 239  |

| 9.2.2.          | Демультиплексор                                  |      |

| 9.2.3.          | · · · · ·                                        |      |

| 9.3. Ана        | логовые мультиплексоры и демультиплексоры        |      |

|                 | ажнения                                          |      |

| Глава 10        | ).                                               |      |

|                 | ые счетчики                                      | 247  |

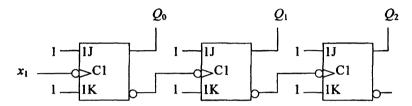

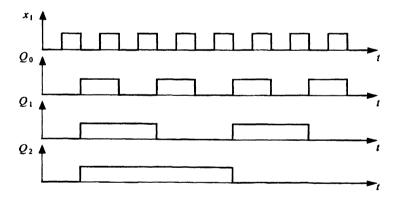

|                 | нхронный счетчик                                 |      |

| 10.1.1.         | <del>-</del>                                     |      |

|                 | Счетчик по модулю 6                              |      |

|                 | Асинхронный обратный счетчик                     |      |

|                 | Временные характеристики асинхронных счетчиков   |      |

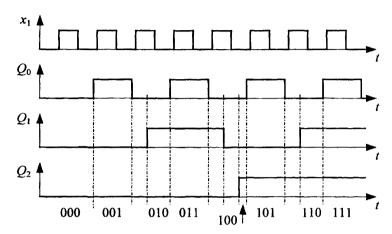

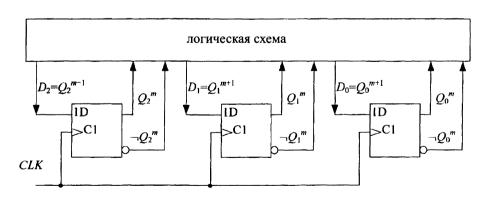

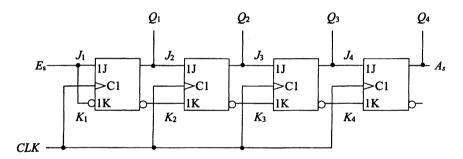

|                 | хронные счетчики                                 |      |

| 10.2.1.         | - ·                                              |      |

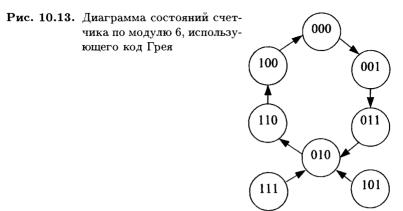

|                 | Счетчик по модулю 6 с использованием кода Грея   |      |

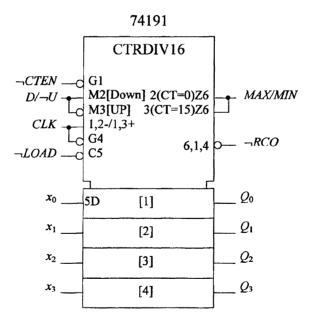

|                 | Синхронный 4-битовый реверсивный двоичный        | 201  |

| 10. <b>2.0.</b> | счетчик 74191                                    | 256  |

| 10.3. Упр       | ажнения                                          |      |

| Глава 11        |                                                  | ,    |

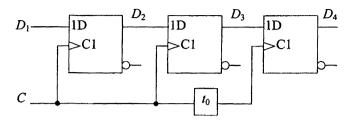

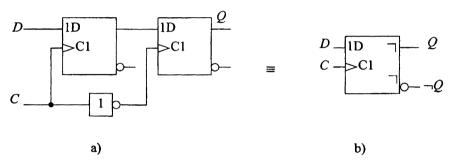

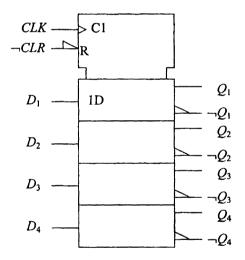

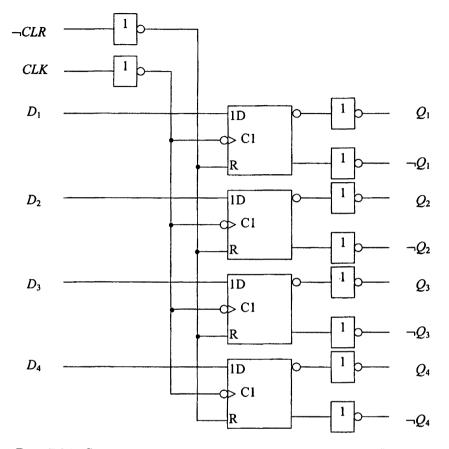

|                 | ·<br>ые регистры                                 | 258  |

|                 |                                                  | 259  |

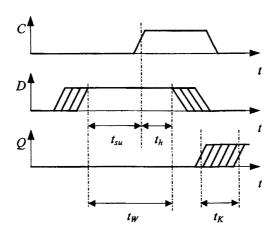

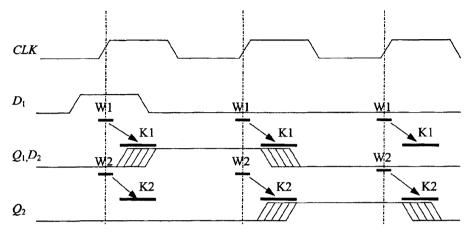

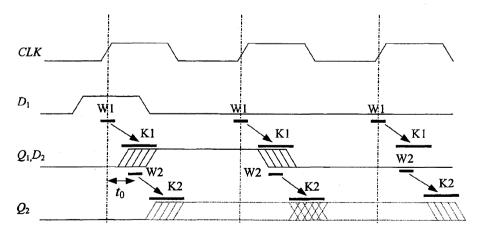

| тил. вое        | менные характеристики слвиговых регистров        | 4.19 |

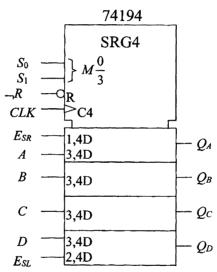

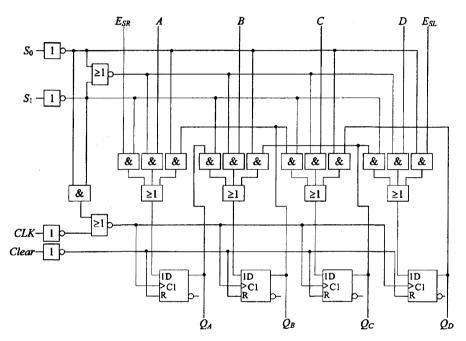

| 11.1.1. Сдвиговый регистр 74194                                  | 261   |

|------------------------------------------------------------------|-------|

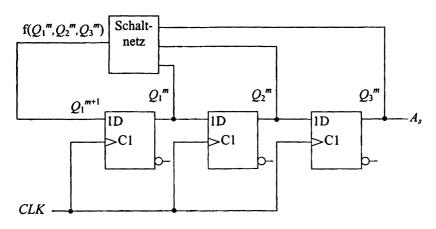

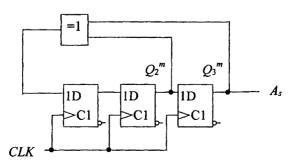

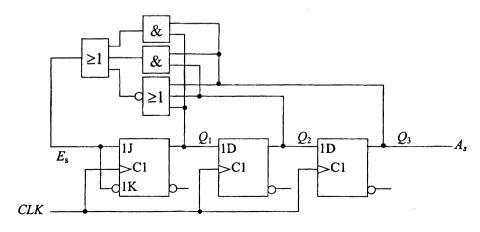

| 11.2. Сдвиговый регистр с обратной связью                        | 262   |

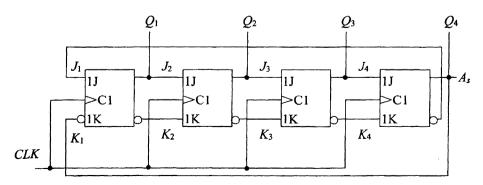

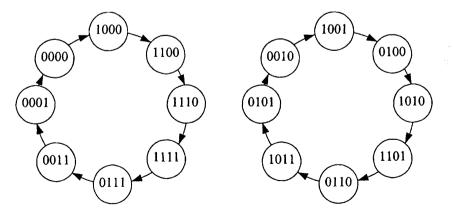

| 11.2.1. Счетчик Мебиуса, счетчик Джонсона                        | 264   |

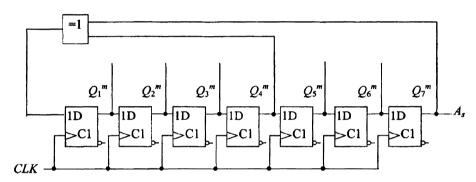

| 11.2.2. Псевдослучайные последовательности                       | 266   |

| 11.3. Упражнения                                                 | 268   |

| Глава 12.                                                        |       |

| Арифметические устройства                                        | 269   |

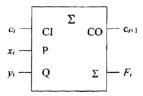

| 12.1. Полный сумматор                                            |       |

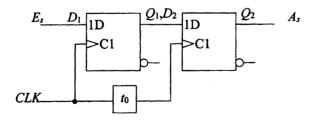

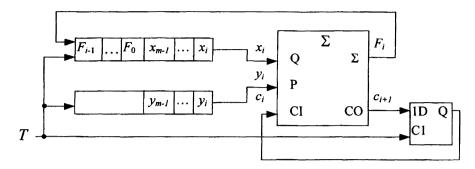

| 12.2. Последовательный сумматор                                  |       |

| 12.3. Сумматор с последовательным переносом (ripple-carry-adder) |       |

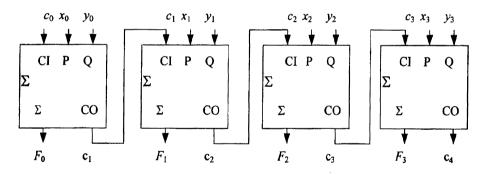

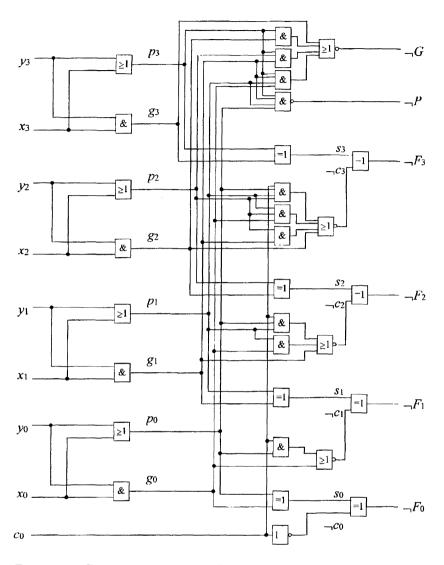

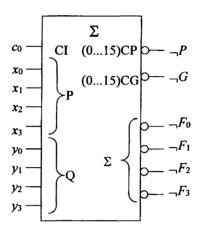

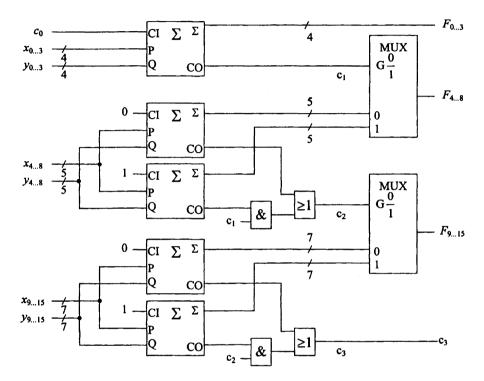

| 12.4. Сумматор с параллельным переносом                          |       |

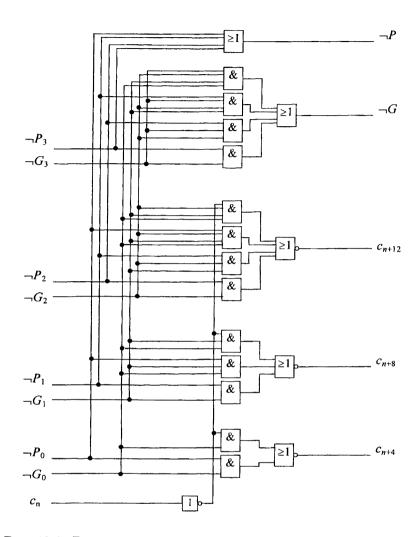

| 12.4.1. Каскадирование сумматоров с параллельным пере-           |       |

| носом                                                            | . 274 |

| 12.4.2. Сравнение сумматоров                                     |       |

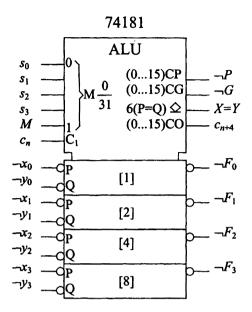

| 12.5. Арифметико-логические вычислительные устройства            |       |

| (ÅLŪ,АЛУ)                                                        | . 276 |

| 12.5.1. Примеры операций                                         |       |

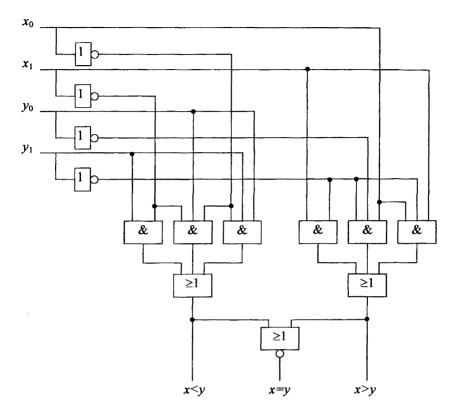

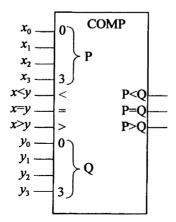

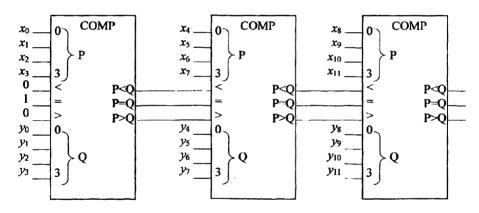

| 12.6. Компараторы                                                | . 283 |

| 12.6.1. 2-битовый компаратор                                     | . 284 |

| 12.6.2. Каскадируемые компараторы                                | . 286 |

| 12.7. Упражнения                                                 | . 286 |

| Глава 13.                                                        |       |

| Цифровые ЗУ                                                      | . 288 |

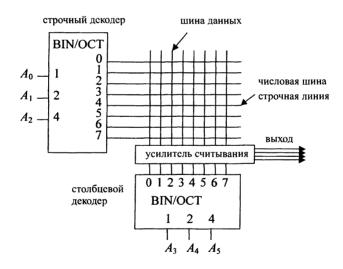

| 13.1. Принципиальная структурная схема ЗУ                        | . 289 |

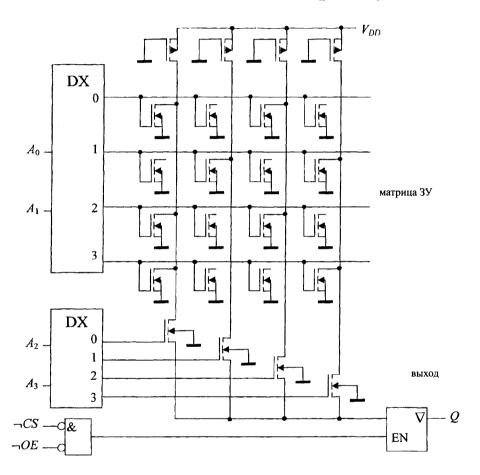

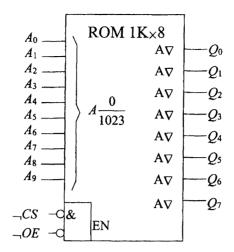

| 13.2. ROM                                                        |       |

| 13.3. PROM                                                       |       |

| 13.4. EPROM                                                      |       |

| 13.5. EEPROM                                                     | . 294 |

| 13.6. EAROM                                                      | . 295 |

| 13.7. NOVRAM                                                     | . 295 |

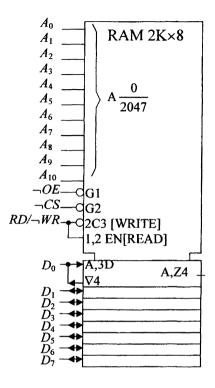

| 13.8. RAM                                                        | . 296 |

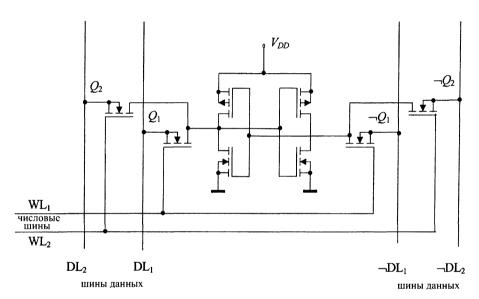

| 13.8.1. Статическое RAM                                          | . 296 |

| 13.8.2. Пример работы RAM                                        | . 297 |

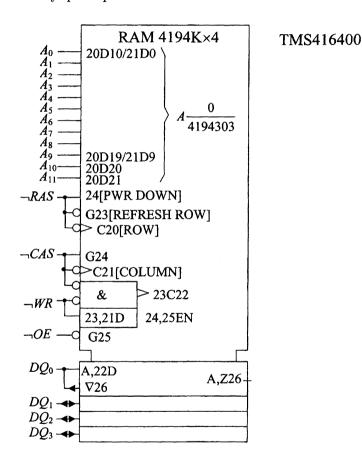

| 13.9. Динамическое RAM                                           | . 301 |

| 13.10. Квазистатическое DRAM                                     | . 306 |

| 13.11. ЗУ «пожарная цепочка»                                     | . 307 |

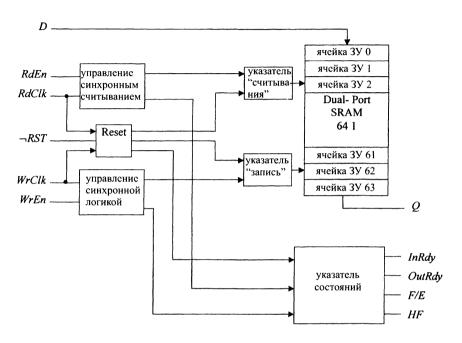

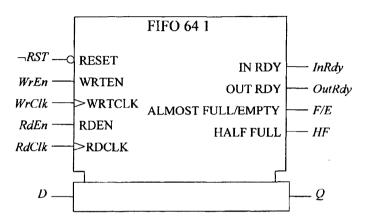

| 13.11.1. Примеры FIFO                                            |       |

| 13.12. Каскадирование ЗУ                                         | . 308 |

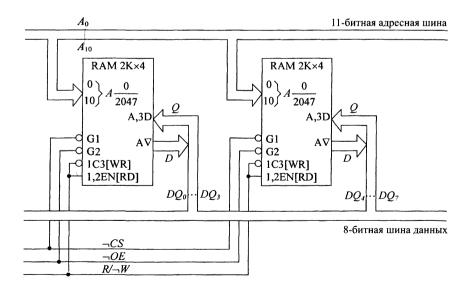

| 13.13. Увеличение длины слов                                     | . 309 |

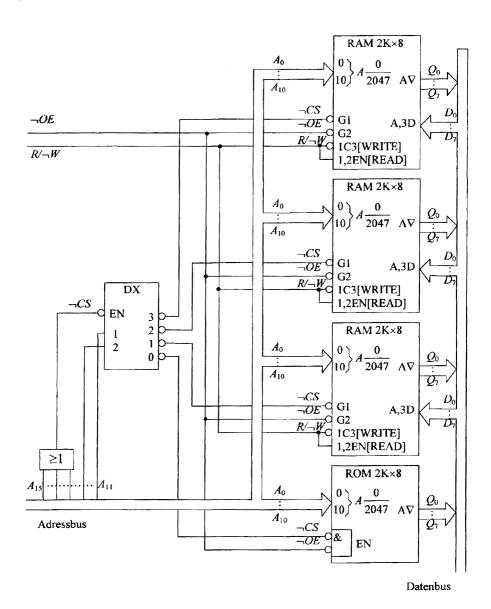

| 13.14. Увеличение емкости ЗV                                     | 300   |

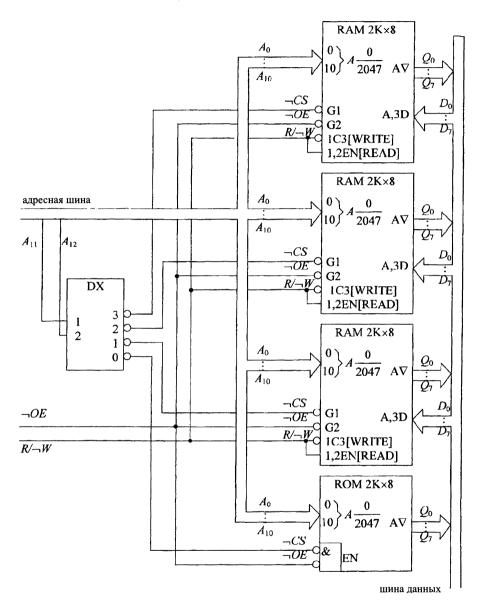

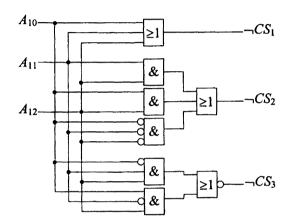

| 13.14.1. Полное декодирование                            | 311 |

|----------------------------------------------------------|-----|

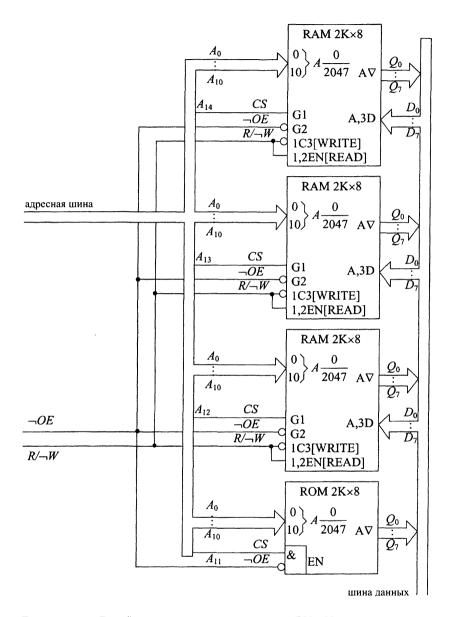

| 13.14.2. Частичное декодирование                         | 312 |

| 13.14.3. Линейное декодирование                          | 314 |

| 13.15. Упражнения                                        | 315 |

| Глава 14.                                                |     |

| Программируемые логические блоки                         | 318 |

| 14.1. Семейства ASIC                                     | 319 |

| 14.2. Программируемые логические ИС (PLD)                |     |

| 14.2.1. Типы PLD                                         |     |

| 14.3. ROM, EPROM, EEPROM                                 |     |

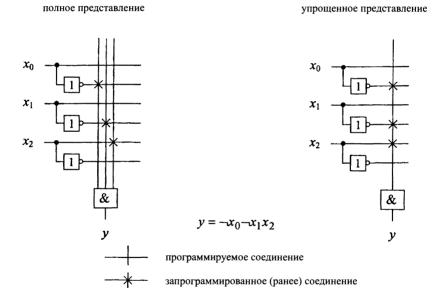

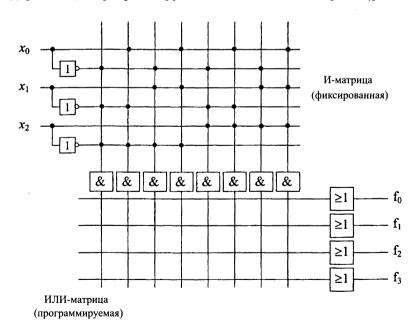

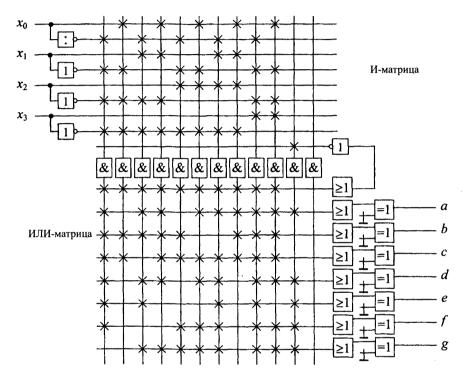

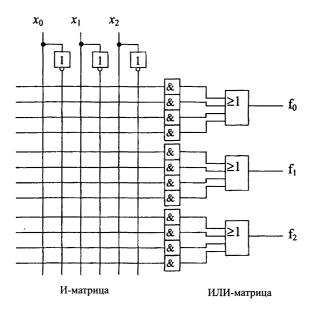

| 14.4. PLA                                                |     |

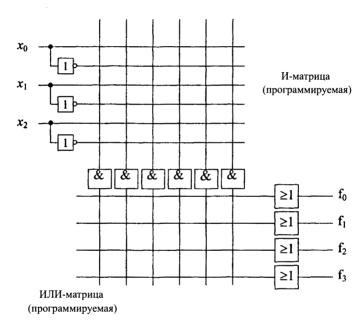

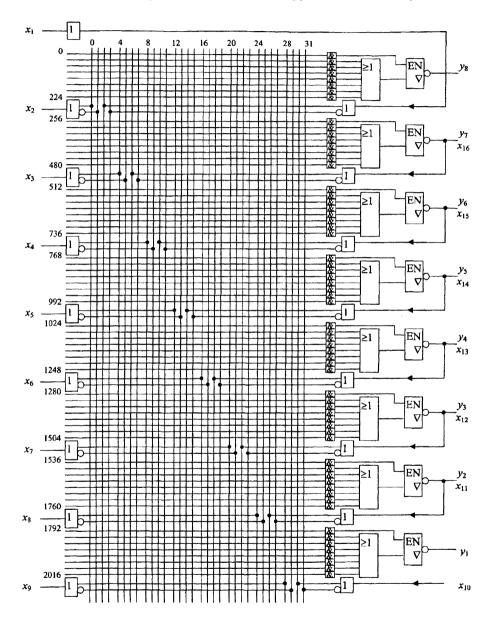

| 14.5. PAL                                                |     |

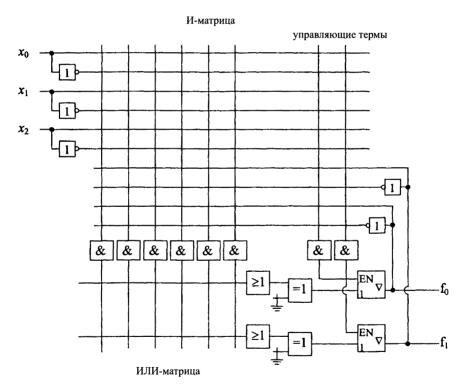

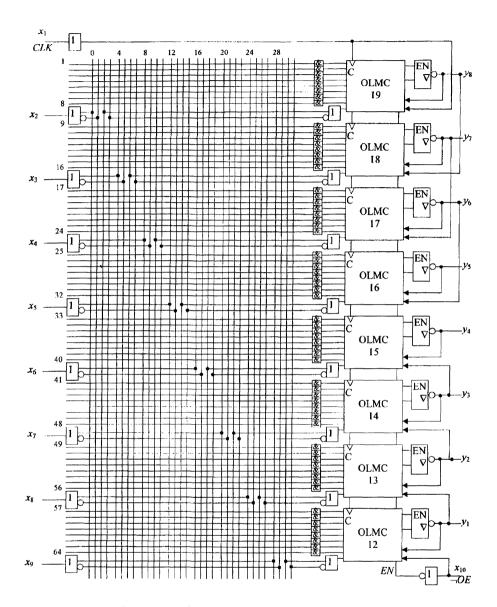

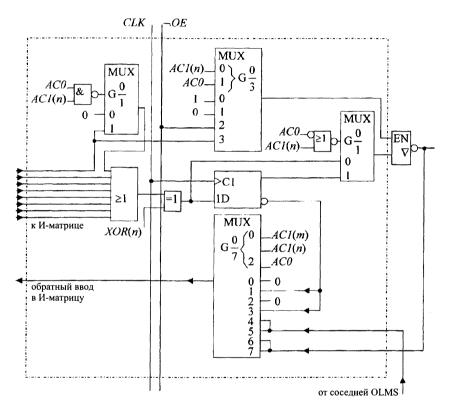

| 14.6. GAL                                                | 334 |

| 14.7. Программирование логических блоков PLD             | 337 |

| 14.7.1. Тестирование                                     | 339 |

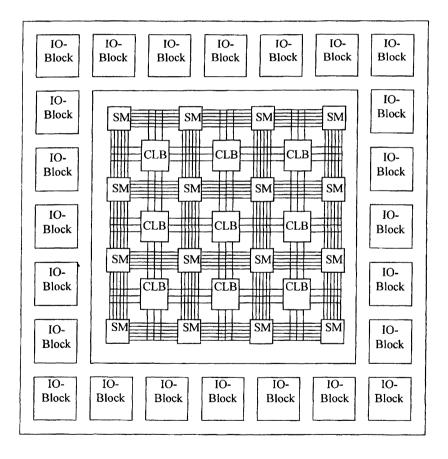

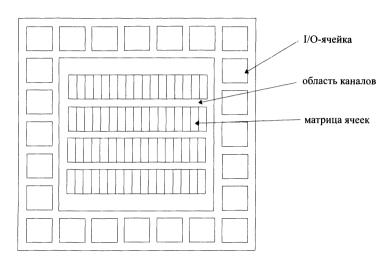

| 14.8. Программируемые полем вентильные матрицы (FPGA)    | 339 |

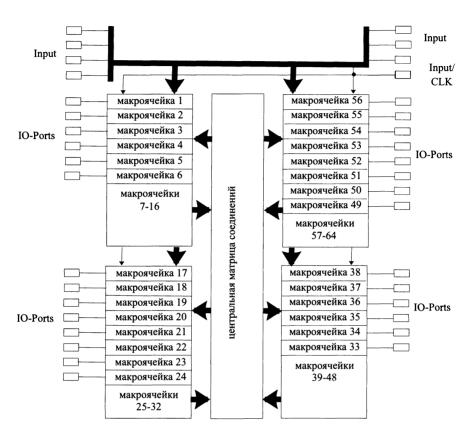

| 14.8.1. Структура FPGA                                   | 340 |

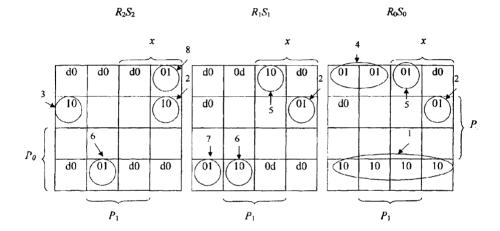

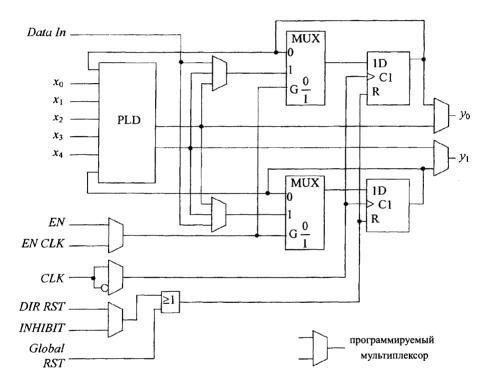

| 14.8.2. Конфигурируемые логические блоки (CLB)           | 342 |

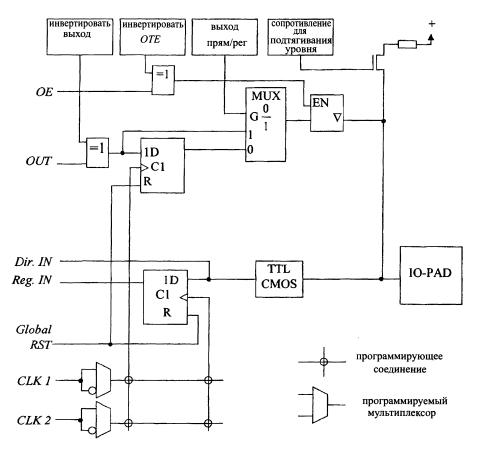

| 14.8.3. ІО-блоки                                         | 342 |

| 14.8.4. Соединительные линии                             | 343 |

| 14.8.5. Программирование FPGA                            | 344 |

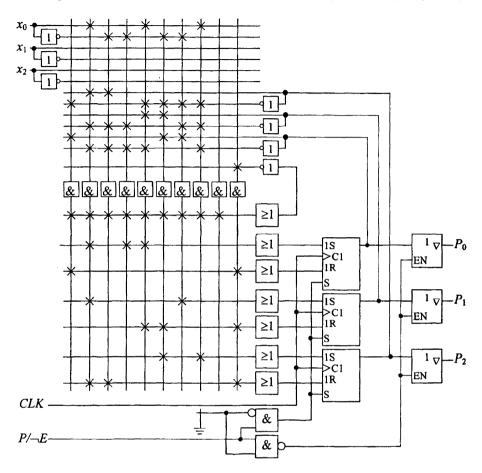

| 14.9. EPLD                                               | 345 |

| 14.9.1. Пример EPLD:CY7C343                              | 345 |

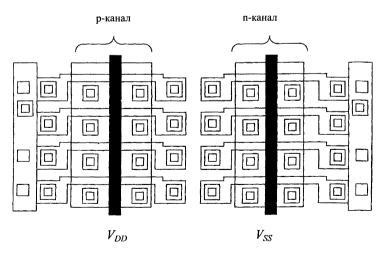

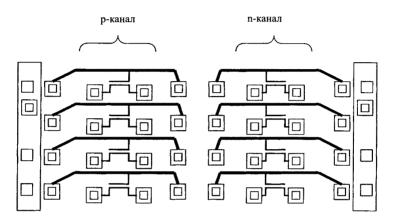

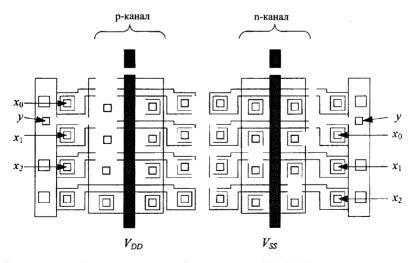

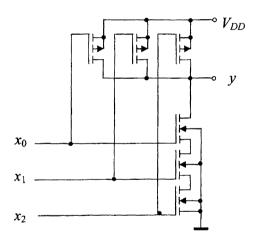

| 14.10. Gate-Arrays                                       | 345 |

| 14.10.1. Структура канализированных вентильных матриц    | 346 |

| 14.11. ASIC со стандартными ячейками                     | 350 |

| 14.12. ASIC на основе полностью заказного проектирования |     |

| 14.13. Упражнения                                        | 351 |

| Глава 15.                                                |     |

| Принципы построения микропроцессоров                     | 353 |

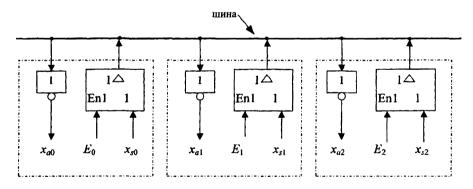

| 15.1. Кооперирующиеся управляющие схемы                  | 353 |

| 15.2. Компьютер фон-Неймана                              |     |

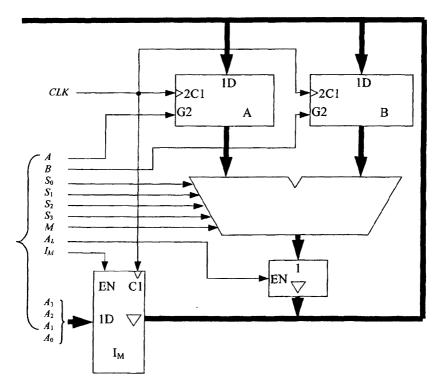

| 15.3. Операционные блоки                                 | 355 |

| 15.3.1. Архитектура операционных блоков                  | 355 |

| 15.3.2. Система шин                                      | 357 |

| 15.4. Управляющие блоки                                  | 358 |

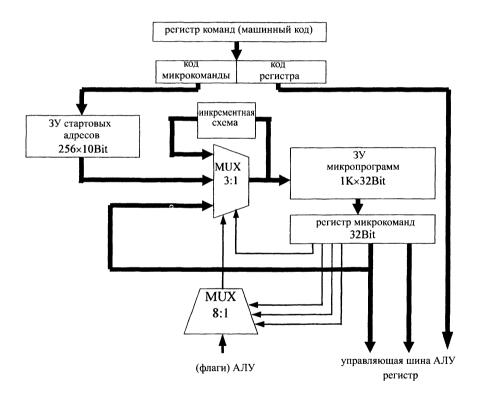

| 15.5. Микропрограммирование                              | 360 |

| 15.6. Упражнения                                         | 362 |

|                                                          | _     |

|----------------------------------------------------------|-------|

| Глава 16.                                                |       |

| Структура, система команд и работа                       |       |

| микропроцессора                                          | 363   |

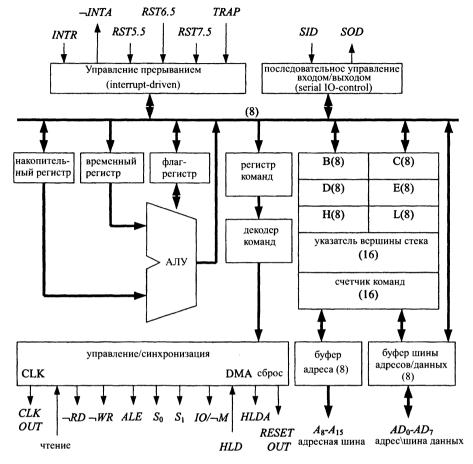

| 16.1. Структура микропроцессора                          | 363   |

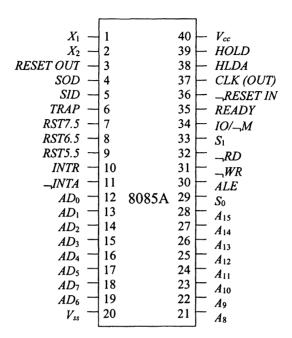

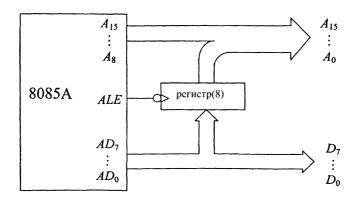

| 16.2. Выводы 8085А                                       |       |

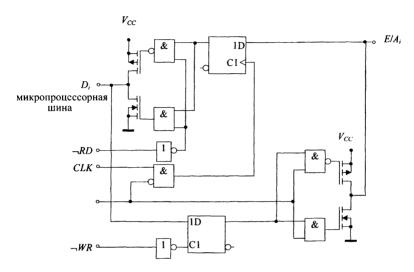

| 16.3. Блоки ЗУ и периферийные блоки                      |       |

| 16.4. Периферийные блоки                                 |       |

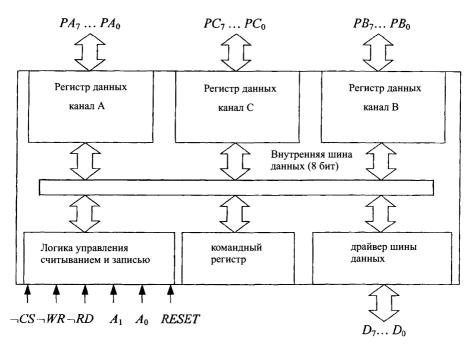

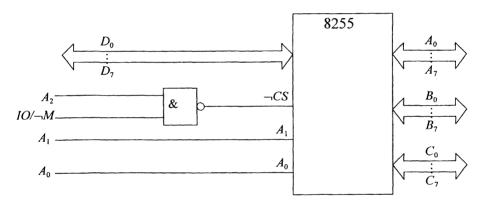

| 16.5. Параллельный интерфейс микропроцессора 8255        |       |

| 16.6. Процесс выполнения команд                          |       |

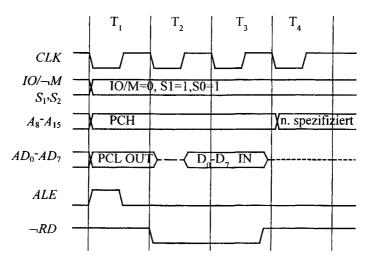

| 16.6.1. Цикл выборки операционного кода (OF)             |       |

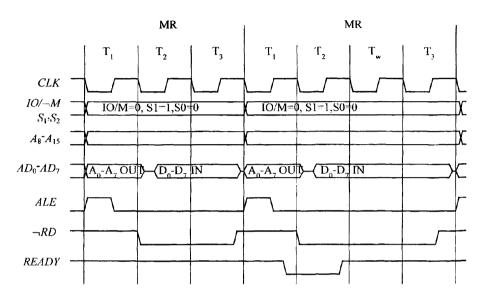

| 16.6.2. Цикл считывания памяти (MR, memory read)         |       |

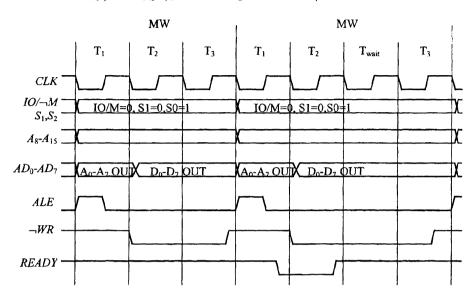

| 16.6.3. Цикл записи в ЗУ (MW, memory write)              |       |

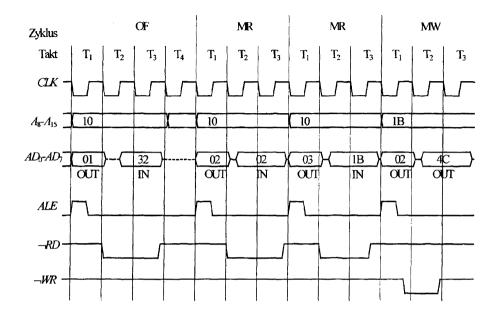

| 16.6.4. Пример выполнения команды                        |       |

| 16.7. Управление с помощью прерывания (interrupt)        | 378   |

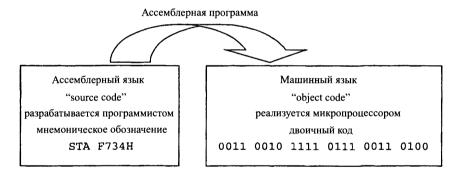

| 16.8. Ассемблерное программирование                      |       |

| 16.9. Набор команд                                       | 380   |

| 16.10. Команда перехода                                  | 381   |

| 16.10.1. Адресация типа «Register»                       | 381   |

| 16.10.2. Адресация типа «Register Indirect»              |       |

| 16.10.3. Адресация типа «Immediate»                      |       |

| 16.10.4. Адресация типа «Direct»                         |       |

| 16.11. Арифметические команды                            | 384   |

| 16.12. Логические операции                               | 386   |

| 16.13. Установка и стирание флагов переноса (carry flag) | 387   |

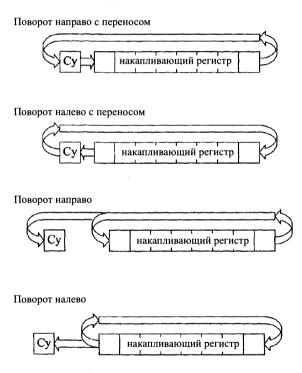

| 16.14. Команды сдвига                                    | 387   |

| 16.15. Разветвление программ                             | 387   |

| 16.15.1. Пример перехода                                 | 388   |

| 16.16. Команды для подпрограммы                          | 389   |

| 16.17. Команды для управления процессором                | 392   |

| 16.18. Ассемблерные команды                              | 394   |

| 16.19. Примеры программ                                  | 397   |

| 16.19.1. Программирование параллельного интерфейса 8255. | 397   |

| 16.19.2. Передача данных в подпрограмму                  | 398   |

| 16.20. Упражнения                                        | 400   |

| А. Приложение                                            | 401   |

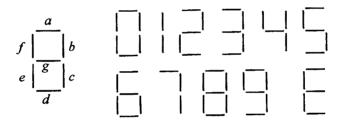

| А.1. Индикация функций                                   |       |

| Решения задач                                            |       |

|                                                          | _ 5 5 |

Литература

427

Список технических терминов

428

#### ГЛАВА І

#### **ВВЕДЕНИЕ**

В последние годы значение цифровой техники все более и более возрастает. Причина этого заключается в значительных преимуществах цифровой техники, при создании очень сложных систем. Это достигается путем представления сигнала двумя значениями, которые могут обрабатываться логическими вентилями с сильно нелинейными передаточными характеристиками без сбоев, накопления и дальнейшего распространения искажений сигнала. Благодаря такому представлению сигналов удалось создать полупроводниковую технологию, позволяющую реализовать до 108 элементов на одном кристалле.

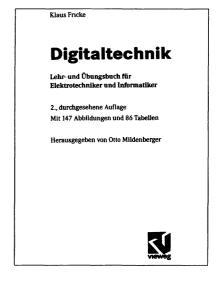

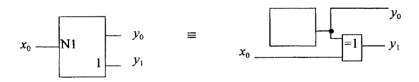

Поскольку целью систем цифровой техники является обработка сигналов, следует несколько подробнее рассмотреть понятие «сигнал». Сигналы служат для переноса информации. Они описываются такими физическими величинами, как напряжение, ток, давление, сила и т. д. Амплитуды таких величин зависят от времени. Передаваемая информация заключается в изменяющихся амплитудных значениях. Пусть, например, измеряется зависящий от времени уровень жидкости F в резервуаре. На рис. 1-1а показана зависимость уровня жидкости от времени. Если датчик выдает электрический сигнал, напряжение которого пропорционально величине заполнения, получаем временную зависимость напряжения  $U_s$ , показанную на рис. 1-1b. Этот сигнал имеет непрерывную величину, то есть в измеряемом диапазоне могут появиться все значения амплитуды.

Системы, которые могут обрабатывать непрерывные по величине сигналы, называются аналоговыми системами.

Дискретные по величине сигналы, которые также называют цифровыми сигналами, могут в отличие от этого принимать только определенные дискретные значения в фиксированные моменты времени. Примером цифрового сигнала является сигнал, который с помощью двух различных уровней напряжения показывает, закрыта или открыта дверь. Подобные сигналы могут непосредственно обрабатываться цифровыми системами.

В том случае, если сигналы с непрерывной величиной должны передаваться цифровыми системами, эти сигналы должны быть пред-

варительно квантизированы. В соответствии с данным процессом, с определенными временными точками (точками считывания) соотнесена амплитуда сигнала дискретной амплитудной ступени. Так сделано на рис.  $1.1\,\mathrm{c}$  для вышеупомянутого примера, в котором показан датчик уровня заполнения. При этом получаем напряжение с дискретными величинами  $U_q$ . При квантизировании необходимо принимать во внимание ошибку округления.

Рис. 1.1. Пример «оцифровывания» сигналов.

- а) Зависимость от времени t уровня наполнения резервуара F.

- b) Зависимость от времени выходного напряжения датчика  $U_s$ .

- с) Квантизированная зависимость от времени напряжения  $U_q$  при 4-х амплитудных ступенях.

- d) Приведение амплитуд в соответствие с записью величин в виде кода 00, 01, 10 и 11.

При цифровой передаче сигнал вначале должен быть переведен в цифровую форму. В этом случае амплитуда будет предъявляться с помощью последовательности цифр. Каждая цифра представляет собой сигнал с дискретным значением. На рис. 1.1 d приведен пример кодирования с помощью двух следующих друг за другом цифр. Амплитудная ступень 0 представлена двумя цифрами. Амплитуды 1, 2 и 3 становятся сочетаниями 01, 10, 11. Следует различать также дискретные во времени сигналы и непрерывные во времени сигналы. Дискретные во времени сигналы могут изменять свою амплитуду только в определенные моменты времени, в то время как непрерывные во времени сигналы могут изменять свою амплитуду

в произвольные моменты времени. Цифровые системы могут быть дискретными во времени, в этом случае их называют синхронными. Синхронизация осуществляется с помощью тактового сигнала.

Благодаря ограничению в использовании конечного числа амплитудных ступеней, цифровая система обладает высокой помехозащищенностью. Подвергнувшиеся воздействию помех цифровые сигналы могут быть однозначно приведены к первоначальным дискретным амплитудным значениям. Но, чтобы не возникла ошибка, помеха не должна превышать половину расстояния между двумя амплитудными ступенями.

Цифровые системы имеют ряд преимуществ перед аналоговыми системами:

- При использовании цифровых сигналов не происходит воспроизведения их искажений, благодаря чему появляется возможность реализации систем любой степени сложности, например, микропроцессоров. Это свойство цифровых систем определяет их превосходство и при передаче на большие расстояния.

- Цифровые системы сравнительно легко проектировать, поскольку способ их описания представляющий собой булеву алгебру аппарат очень удобный для автоматизации. Сегодня разработка сложных цифровых систем автоматизирована посредством применения высокопроизводительных алгоритмов.

- Цифровые системы можно относительно просто тестировать.

#### Недостаток цифровых систем:

– Цифровые системы являются более медленными системами, чем аналоговые. Поэтому в области высоких частот доминирует аналоговая техника.

#### ГЛАВА 2

## КОДИРОВАНИЕ И СИСТЕМЫ СЧИСЛЕНИЯ

#### 2.1. Коды

В цифровой технике коды используются для того, чтобы оптимально представить сигнал для какого-либо случая применения. Код отображает символы одного множества через символы второго множества. При этом должна существовать возможность декодирования, чтобы из кодированных символов можно было получить исходные символы.

Известным примером кода является код Морзе. Определение кода производится с помощью таблицы соответствия. Для кода Морзе подобное соответствие отображено в табл. 2.1. Этот код является обратимым, поскольку из буквы можно получить символ Морзе, а из него можно вновь образовать букву. Но это справедливо только для текста, который написан строчными буквами, поскольку код Морзе не делает различия между прописными и строчными буквами. Строго говоря, из кода Морзе нельзя восстановить путем декодирования текст, записанный с помощью строчных и прописных букв.

| Таблица : | 2.1. | Код | Морзе. |

|-----------|------|-----|--------|

|-----------|------|-----|--------|

| Алфавит | Код Морзе | Алфавит | Код Морзе | Алфавит | Код Морзе |

|---------|-----------|---------|-----------|---------|-----------|

| a       | •         | j       |           | s       |           |

| b       |           | k       | ·         | t       | -         |

| c       | - • • •   | l       |           | u       |           |

| d       | - • •     | m       |           | v       | • • • –   |

| e       | •         | n       | - •       | w       |           |

| f       |           | 0       |           | x       |           |

| g       |           | p       |           | y       |           |

| h       |           | q       |           | z       |           |

| I       |           | r       |           |         |           |

Для каждого применения имеется более или менее подходящий код. Так для проведения операций над числами в компьютере рационально применять другой код, чем для передачи чисел по линии связи. В данной главе исследуются различия между отдельными кодами и даны указания по их специфическому применению.

Комбинацию нескольких символов кода называют словом (word). В последующем мы ограничимся технически важным случаем, в котором все слова одного кода имеют одинаковую длину n. В коде Морзе этот случай не имеет места. Если в код входит множество символов N, то  $N^n$  различных слов могут иметь длину n. Если используются все  $N^n$  возможных слов одного кода, то в этом случае говорят о минимальном коде. Если используют менее чем  $N^n$  слов, то его называют избыточным кодом. Ниже можно найти описание наиболее употребительных кодов, полное описание можно получить из [8].

#### 2.2. Двоичный код

Двоичный код является важнейшим кодом в цифровых системах, поскольку он является универсальным. Благодаря ограничению, в соответствии с которым применяются только символы 1 и 0, становится возможной обработка сигналов с помощью схемных элементов, работающих как переключатели. Двоичный код позволяет также пользоваться арифметикой, аналогичной арифметике десятичных систем. Двоичную систему счисления можно рассматривать как кодирование десятичной системы. Двоичное число состоит из слова, которое образовано символом  $C_i \in \{0,1\}$ . Символы  $C_i$  одного слова называют в цифровой технике битами. Слово z в двоичном представлении формируется путем последовательного присоединения отдельных битов, как это показано ниже:

$$z_B = c_{n-1}c_{n-2}\cdots c_1c_0, c_{-1}c_{-2}\cdots c_{-m+2}c_{-m+1}c_{-m}$$

(2.1)

Двоичное число имеет n разрядов перед запятой и m разрядов после запятой. Отдельным битам присвоены, в соответствии с их позицией i в слове, весовые коэффициенты  $2^i$ . На основе этого можно рассчитать эквивалентное десятичное число  $z_{10}$ :

$$z_D = g(z_B) =$$

$$= c_{n-1}2^{n-1} + c_{n-2}2^{n-2} + \dots + c_12^1 + c_02^0 + c_{-1}2^{-1} + \dots + c_{-m}2^{-m}$$

(2.2)

Рассмотрим в качестве примера двоичное число  $10110,001_B$ , которое как двоичное число отмечено символом B (binary). Оно интерпретируется как:

$$g(z_2) = 1 \cdot 2^4 + 0 \cdot 2^3 + 1 \cdot 2^2 + 1 \cdot 2^1 + 0 \cdot 2^0 + 0 \cdot 2^{-1} + 1 \cdot 2^{-2} + 1 \cdot 2^{-3} = z_{10} = 22,375_{10}$$

Двоичный (или дуальный) код обозначается как взвешенный код, поскольку стоящие дальше влево биты обладают более высокими весовыми коэффициентами. Уравнение (2.2) можно рассматривать как правило, в соответствии с которым производится преобразование двоичных чисел в десятичные числа.

Преобразование десятичных чисел в двоичные числа является более сложным. Оно может быть описано различными алгоритмами для целочисленной и дробной частей. В приведенном выше примере с числом  $22,375_{10}$  алгоритм должен быть представлен следующим образом:

• Вначале формируется целочисленная часть двоичного числа. Для этого целочисленная часть десятичного числа последовательно делится на 2 и записывается остаток, пока не будет получен 0.

$$22:2=1$$

остаток  $0$  тен неготивной и  $2:2=1$  остаток  $0$  остато

Соответствующее числу  $22_{10}$  двоичное число представляет собой  $10110_2$ .

• Второй шаг заключается в преобразовании дробной части десятичного числа в дробную часть двоичного числа. Вначале дробная часть десятичного числа умножается на 2. Целочисленная часть отделяется, она образует разряды двоичного числа с наименьшими значениями.

Процесс повторяется, как это показано ниже.

В этом примере мы видим, что остаток равен 0. Но не обязательно так всегда бывает. В нормальном случае дробная часть эквивалентного двоичного числа имеет бесконечно большое количество разрядов. В этом случае необходимо удовольствоваться определенным числом разрядов после запятой и ограничить этим точность. В нашем случае  $0,375_{10}$  точно соответствует  $0,011_2$ .

На основе целочисленной и дробной частей получаем искомое двоичное число  $10110,011_2.$

## 2.3. Арифметические операции с фиксированной запятой в двоичной системе

В данной главе описываются арифметические операции с числами с фиксированной запятой. Арифметические операции с фиксированной запятой означают, что в них запятая всегда стоит на фиксированном месте. При этом место, на котором стоит запятая, ориентируется на позицию в 3У, на которой находится число. В этом случае нет необходимости реализовать запятую в аппаратуре компьютера. Она существует только в голове программиста. Мы ограничиваемся постоянной длиной слова n, как это имеет место в компьютерах. На основе этого можно обсудить проблему переполнения допустимой области.

#### 2.3.1. Целочисленное сложение в двоичной системе

Целочисленное сложение двух чисел A и B производится в двоичной системе точно так же, как и в десятичной системе — по разрядам. Как и там, в каждом разряде должны быть просуммированы обе двоичных цифры  $a_n$  и  $b_n$  и перенос из предыдущего разряда  $C_{n-1}$ .

При сложении возникают (табл. 2.2) новая сумма  $S_n$  и новый перенос  $C_n$ .

В этой таблице дискретной линией разделены входные и выходные величины. Например:

$$+\frac{011111110}{00110101}$$

$=10110011$

перенос  $1111100$

Необходимо следить, чтобы в приведенном выше примере суммировались два числа длиной по 8 бит и чтобы итог тоже имел длину 8 бит, чтобы не было переполнения допустимой зоны.

**Таблица 2.2.** Сложение в двоичной системе со слагаемыми  $a_n,b_n$ и переносом из предыдущего разряда  $C_{n-1}$ . Сумма равна  $S_n$ , новый перенос  $C_n$ .

| $\mathbf{a}_n$ | $\mathbf{b}_n$ | $c_{n-1}$ | $\mathbf{c}_n$ | $\mathbf{s}_n$ |

|----------------|----------------|-----------|----------------|----------------|

| 0              | 0              | 0         | 0              | 0              |

| 0              | 0              | 1         | 0              | 1              |

| 0              | 1              | 0         | 0              | 1              |

| 0              | 1              | 1         | 1              | 0              |

| 1              | 0              | 0         | 0              | 1              |

| 1              | 0              | 1         | 1              | 0              |

| 1              | 1              | 0         | 1              | 0              |

| 1              | 1              | 1         | 1              | 1              |

#### 2.3.2. Сложение чисел с фиксированной запятой

В этом случае, когда суммируются два числа с фиксированной запятой, важным моментом является то, чтобы аналогично обычной процедуре в десятичной системе обе запятые стояли друг над другом. Так, при сложении двух чисел длиной в 8 бит запятая у обоих чисел должна стоять, например, на третьем месте.

Например:

$$\frac{ + 01100,010}{00110,111} = 1100,110$$

перенос 10011,001

#### 2.3.3. Представление с помощью обратного кода

Для того, чтобы иметь малые затраты на аппаратурную часть (hardware) компьютера, были предприняты усилия по сведению к одному алгоритму вычитания и сложения. Этого можно добиться, если применять двоичные цифры в их дополняющей форме. Различают единичное дополнение (обратный код, поразрядное дополнение) и двойное дополнение (точное дополнение).

Поразрядное дополнение формируется путем замены всех нулей на единицы и обратно. Следовательно, поразрядным дополнением (one's complement) 0001 является 1110. Ниже поразрядное дополнение двоичного числа A обозначено  $\neg A$ . Очевидно, что при представлении n-битового слова имеем:

$$\neg A + A = 2^n - 1 \tag{2.3}$$

Например, при представлении 8-битового слова имеем:

$$10110011 + 01001100 = 11111111 = 2^8 - 1$$

Можно так преобразовать уравнение (2.3), чтобы получить формулу для расчета поразрядного дополнения:

$$\neg A = 2^n - 1 - A \tag{2.4}$$

### 2.3.4. Представление с помощью двойного дополнения (точное дополнение, two's complement)

Точное дополнение  $A_{K2}$  образуется из поразрядного дополнения  $\neg A$  путем прибавления 1:

$$A_{K2} = \neg A + 1 \tag{2.5}$$

Следовательно, с учетом (2.4) будет справедливо:

$$A_{K2} = 2^n - A (2.6)$$

Мы видим, что в данном представлении содержится «-A», благодаря чему оно удобно для проведения вычитания. Учтем также, что  $2^n$  в двоичном представлении имеет n+1 разрядов. Ниже пример точного дополнения для 10101100:

$$A_{K2} = \neg A + 1 = 01010011 + 1 = 01010100$$

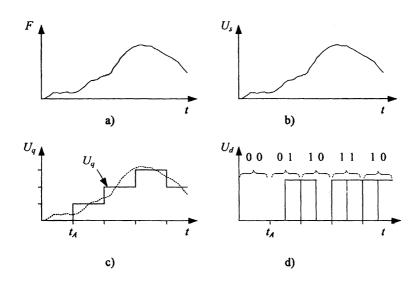

Представление 4-битовых двоичных слов в круговой форме, приведенное на рис. 2.1, позволяет показать числовой диапазон. Соответствующее данным значениям набольшее представляемое положительное число равно  $7_D$ , соответствующее данным значениям наибольшее отрицательное число равно  $-8_D$ . Следовательно, числовой диапазон построен несимметрично, поскольку отрицательное число занимает больше места, чем положительное. Наибольшее и наименьшее представляемые числа можно выразить как:

$$z_{max} = 2^{n-1} (2.7)$$

$$z_{min} = -2^{n-1} (2.8)$$

На рис. 2.1 можно видеть, что малые числа, сформированные на основе точного дополнения, содержат много ведущих единиц, когда они отрицательны, и содержат много ведущих нулей, когда они

положительны. Соответствующие данным значениям большие числа, сформированные на основе точного дополнения, содержат далеко влево отстоящий нуль, когда они отрицательны, и далеко влево отстоящий нуль, когда они положительны. Их собственным точным дополнением является число  $1000_B\ (-8_D)$ . Важно установить, что при представлении на основе точного дополнения имеем только один 0. Это облегчает запрос, равен ли результат 0. Напротив, при представлении на основе поразрядного дополнения имеют место двоичное число  $0000_B$ , соответствующее  $+0_D$  и двоичное число  $1111_B$ , соответствующее  $-0_D$ .

Рис. 2.1. Представление 4-битовых слов с помощью 4-битового дополнения.

## 2.3.5. Вычитание при представлении с помощью точного дополнения

Пусть должны были вычтены одно из другого два положительных двоичных числа A и B. При условии применения точного дополнения в соответствии с уравнением (2.6) вычитание можно провести следующим образом:

$$A - B = A - B + B_{K2} - B_{K2} = A - B + B_{K2} - (2^{n} - B)$$

(2.9)

Раскрытие скобок в правой части уравнения дает:

$$A - B = A + B_{K2} - 2^n (2.10)$$

Что означает вычитание  $2^n$ ? Поясним это на примере операции вычитания 7-3=4 в 4-битовой двоичной системе. Сумма двоичного

эквивалента числа 7 и дополнение двоичного эквивалента числа 3 равняется:

$$\begin{array}{rrrr}

+ & 01111 & 7_{10} \\

11101 & -3_{10}

\end{array}$$

$$= 10100 \\

- 10000 \\

= 0100 & 4_{10}$$

Вычитание числа  $10000_B$ , проведенное в соответствии с уравнением (2.10), дает правильный результат  $0100_B$ . Это может произойти в 4-битовом компьютере просто потому, что высший результат игнорируется. Итак, при проведении вычитания с помощью точного дополнения нет необходимости учитывать высший перенос  $c_4$ . Но необходимо соблюдать осторожность в связи с переполнением числового диапазона. Исследуем это ниже.

#### 2.3.6. Переполнение числового диапазона

Исходя из вышесказанного возникает необходимость рассмотрения проблемы переполнения числового диапазона (overflow) в связи с представлением на основе точного дополнения. Переполнение числового диапазона может происходить только в двух случаях. А именно, когда суммируются два положительных числа либо суммируются два отрицательных числа. В связи с этим рассмотрим несколько примеров, относящихся к 4-битовому представлению.

• Пример переполнения числового диапазона при сложении двух положительных чисел:

Очевидно, что результат является неправильным. Ошибка возникает за счет переноса 3-го разряда на место 4-го разряда, что приводит к симуляции отрицательного числа. Этот перенос  $c_3$  в представлении, использующем n бит, обычно обозначается как  $c_{n-1}$ . Перенос  $c_4$  (в общем случае  $c_n$ ) из разряда 4 в разряд 5 называется Carry (Cy). В этом примере данный перенос не имеет места.

Пример переполнения численного диапазона при сложении отрицательных чисел:

$$\begin{array}{rrrr}

+ & 1011 & -5_{10} \\

1011 & -5_{10} \\

\hline

= (1)0110 & 6_{10}

\end{array}$$

В этом примере также появляется неправильный результат. Имел место не перенос  $c_{n-1}$  из разряда 3 в разряд 4, а перенос  $c_n$  из разряда 4 в разряд 5.

• Для сравнения проведем сложение двух отрицательных чисел без переполнения числового диапазона:

$$\begin{array}{rrrr}

+ & 1111 & -1_{10} \\

1101 & -3_{10} \\

\hline

= (1)1100 & -4_{10}

\end{array}$$

Имели место переносы  $c_n$  и  $c_{n-1}$ .

Сведем эти результаты вместе с другими, здесь не показанными случаями, в таблицу. На основе результатов, представленных в табл. 2.3, для двух двоичных чисел A и B, которые лежат в числовом диапазоне, определяемом n-битовом представлением на базе точного дополнения, можно установить перенос переполнения при сложении.

**Таблица 2.3.** Перенос переполнения при сложении в случае *n*-битового представления на основе точного дополнения.

|       | Правильный результат    | Перенос переполнения    |

|-------|-------------------------|-------------------------|

| A + B | $c_n = 0,  c_{n-1} = 0$ | $c_n = 0, c_{n-1} = 1$  |

| A-B   | $c_n = c_{n-1}$         | невозможен              |

| -A-B  | $c_n = 1, c_{n-1} = 1$  | $c_n = 1,  c_{n-1} = 0$ |

Следовательно, правильный результат имеет место тогда, когда  $c_n=c_{n-1}$ , неправильный результат — когда  $c_n \neq c_{n-1}$ .

#### 2.3.7. Умножение

Умножение выполняется так же, как и для десятичной системы. Рассмотрим пример умножения на основе двоичной системы для чисел

$$10_D \times 11_D = 110_D$$

:

$$\begin{array}{r}

\times 1010 \\

\hline

1011 \\

\hline

1010 \\

1010 \\

\hline

1010 \\

\hline

1110110

\end{array}$$

Наибольший из ожидаемых результатов E умножения двух n-битовых слов представляет собой:

$$E = (2^{n} - 1) \cdot (2^{n} - 1) = 2^{2n} - 2^{n+1} + 1 \le 2^{2n} - 1$$

Следовательно, результат умножения двух n-битовых чисел имеет длину 2n бит. Но он меньше, чем максимальное представляемое с помощью 2n бит двоичное число  $2^{2n}-1$ .

Сказанное выше справедливо для умножения положительных чисел. При вычислениях с использованием представления на основе точного дополнения могут быть применены специальные алгоритмы [20], или следует числа на основе точного дополнения перед умножением преобразовать обратно в исходные значения, а результат перевести в соответствии со знаком в желаемое представление.

При умножении чисел с фиксированной запятой вначале числа умножаются без учета запятой. Затем запятая вводится в соответствии с правилом: умножение двух чисел с n и k разрядами после запятой даст произведение с n+k разрядами после запятой.

#### 2.3.8. Деление

Для деления можно использовать тот же самый алгоритм, что и в десятичной системе. Продемонстрируем это на примере уравнения  $10_D:2_D=5_D$ :

Соответственно при делении числа с n разрядами после запятой на число с k разрядами после запятой частное имеет n-k разрядов

после запятой. Так в соответствии с верхним примером имеем:

$$10, 10 \cdot 101, 1 = 1101, 110$$

Деление чисел с точным дополнением также можно свести к умножению и сложению [20].

#### 2.4. Шестнадцатеричный код

На практике наряду с двоичным кодом внедрился шестнадцатеричный код, поскольку он обеспечивает лучшее обозрение длинных двоичных чисел. Шестнадцать шестнадцатеричных цифр определены в табл. 2.4. Шестнадцатеричные цифры больше девяти представлены буквами A–F. Для преобразования двоичных в шестнадцатеричные числа объединяют по четыре цифры двоичного числа, которые интерпретируются как шестнадцатеричный разряд. Благодаря этому шестнадцатеричное число занимает только четверть разрядов, занимаемых двоичным числом одинаковой величины.

Например:

Итак, справедливо выражение  $0110011001111_2 = GCF_{16}$ .

| десятичные | двоичные | шестнадца-<br>теричные | десятичные | двоичные | шестнадца-<br>теричные |

|------------|----------|------------------------|------------|----------|------------------------|

| 0          | 0000     | 0                      | 8          | 1000     | 8                      |

| 1          | 0001     | 1                      | 9          | 1001     | 9                      |

| 2          | 0010     | 2                      | 10         | 1010     | A                      |

| 3          | 0011     | 3                      | 11         | 1011     | В                      |

| 4          | 0100     | 4                      | 12         | 1100     | C                      |

| 5          | 0101     | 5                      | 13         | 1101     | D                      |

| 6          | 0110     | 6                      | 14         | 1110     | E                      |

| 7          | 0111     | 7                      | 15         | 1111     | F                      |

Таблица 2.4. Шестнадцатеричные числа.

В качестве обозначения шестнадцатеричного числа используется индекс H. Преобразование шестнадцатеричного числа в десятичное число и обратно проще всего производить через соответствующее двоичное число. Также возможно производить преобразование с помощью алгоритма, как при преобразовании двоичного числа в

десятичное число. Обратное преобразование производится аналогично представленному уравнением (2.2).

#### 2.5. Восьмеричный код

Восьмеричный код применяется аналогично шестнадцатеричному, только объединяются лишь по 3 разряда двоичного числа. Для восьмеричного кода применяются цифры десятичного кода от 0 до 7, он обозначается индексом 0.

Например:

Следовательно, справедливо  $11010100011_2 = 6543_8$ .

#### 2.6. Код Грея

Часто в цифровой технике требуется для числового кода схема кодирования, в соответствии с которой при переходе от одного числа к следующему изменялась бы только одна цифра. Выполнение этого условия необходимо, когда вследствие технических неточностей момент переключения не может быть точно выдержан. При переключении двух цифр из-за этого могут возникнуть неправильные коммутационные операции. В качестве примера подобной ошибки рассмотрим переключение от  $1_{10}$  к  $2_{10}$  в двоичном коде:

При этом переключении изменяются биты 0 и 1 при одновременном переключении непосредственно достигается новое число. Если вначале изменяется бит 0, то появляется число 0000, и только когда изменяется бит 1, получаем правильное число 0010. Если же сначала изменяется бит 1 и потом изменяется бит 0, то в промежутке возникает число 0011. Коды Грея позволяют избежать этой очень серьезной ошибки за счет того, что при переходе от одного кодового слова к следующему изменяется только один разряд. В табл. 2.5 представлен 4-разрядный код Грея. В дополнение к вышесказанному показанный код имеет свойство, которое заключается в его цикличности, так как также и при переходе от высшего числа (15D)

низшему числу изменяется только один разряд. Циклические коды Грея могут быть сконструированы для всех прямых длин периодов.

| Десятичные (числа) | Код Грея | Десятичные (числа) | Код Грея |

|--------------------|----------|--------------------|----------|

| 0                  | 0000     | 8                  | 1100     |

| 1                  | 0001     | 9                  | 1101     |

| 2                  | 0011     | 10                 | 1111     |

| 3                  | 0010     | 11                 | 1110     |

| 4                  | 0110     | 12                 | 1010     |

| 5                  | 0111     | 13                 | 1011     |

| 6                  | 0101     | 14                 | 1001     |

| 7                  | 0100     | 15                 | 1000     |

Таблица 2.5. Пример 4-разрядного кода Грея.

#### 2.7. Двоично – десятичный код

Если мы хотим подвести к десятичным цифрам некоторые отметки, то для этого подойдет код, в котором отдельным десятичным цифрам приданы двоично-кодированные кодовые слова. Этот код обозначается как двоично-десятичный код (ВСD-код). Подходящая возможность реализации заключается в том, чтобы представить через соответствующую каждой из них 4-разрядную двоичную цифру. Поскольку отдельные разряды имеют веса 8, 4, 2 и 1, данный код называют кодом типа 8-4-2-1. Существует также возможность построить двоично-десятичный код 2, 4, 2, 1 (Aiken-Code). К другим двоично-десятичным кодам относятся код с избытком три (3-Excess-Code) и двоично-десятичный код Грея (ВСD-Gray-Code) [5].

| Десятичная цифра | Код типа 8-4-2-1 | Десятичная цифра | Код типа 8-4-2-1 |

|------------------|------------------|------------------|------------------|

| 0                | 0000             | 5                | 0101             |

| 1                | 0001             | 6                | 0110             |

| 2                | 0010             | 7                | 0111             |

| 3                | 0011             | 8                | 1000             |

| 4                | 0100             | 9                | 1001             |

Таблица 2.6. Двоично-десятичный код.

#### 2.8. Алфавитно – цифровые коды

Существует большое количество кодов, осуществляющих представление алфавитно-цифровых символов с помощью двоичных цифр. Известным примером подобных символов является код ASCII (American Standard Code for Information Interchange), который содержит также ряд управляющих символов.

| ASCII | ASCII |

|-------|-------|

| 00    | 10    |

| 01    | 11    |

| 02    | 12    |

| 03    | 13    |

| 04    | 14    |

| 05    | 15    |

| 06    | 16    |

| 07    | 17    |

| 08    | 18    |

| 09    | 19    |

| 0A    | 1A    |

| 0B    | 1B    |

| 0C    | 1C    |

| 0D    | 1D    |

| 0E    | 1E    |

| 0F    | 1F    |

**Таблица 2.7.** Код ASCII (ч.1, управляющие символы)

#### 2.9. Упражнения

**Задача 2.1.** Преобразуйте следующие двоичные числа в десятичные числа:

- a) 1110, 101

- б) 10011, 1101

Задача 2.2. Преобразуйте следующие десятичные числа в двоичные числа:

- a) 22, 125

- б) 45, 33

**Задача 2.3.** Рассчитайте приведенные ниже примеры с использованием точных дополнений при длине слова в 6 бит. Укажите, имеет ли место переполнение числового диапазона.

- a) 010101 001010

- 6) -010111 011011

Задача 2.4. Рассчитайте в двоичной системе:

- a) 110101 · 010101

- 6) 1101110 : 110

Задача 2.5. Разработайте циклический код Грея с длиной периода 6.

**Таблица 2.8.** Код ASCII (ч.2).

| ASCII |    | ASCII |   | ASCII |              | ASCII |   | ASCII |   | ASCII |              |

|-------|----|-------|---|-------|--------------|-------|---|-------|---|-------|--------------|

| 20    | SP | 30    | 0 | 40    | @            | 50    | Р | 60    | ' | 70    | p            |

| 21    | !  | 31    | 1 | 41    | A            | 51    | Q | 61    | a | 71    | q            |

| 22    | "  | 32    | 2 | 42    | В            | 52    | R | 62    | b | 72    | r            |

| 23    | #  | 33    | 3 | 43    | $\mathbf{C}$ | 53    | S | 63    | c | 73    | s            |

| 24    | \$ | 34    | 4 | 44    | D            | 54    | Т | 64    | d | 74    | t            |

| 25    | %  | 35    | 5 | 45    | E            | 55    | U | 65    | е | 75    | u            |

| 26    | &  | 36    | 6 | 46    | F            | 56    | V | 66    | f | 76    | v            |

| 27    | ,  | 37    | 7 | 47    | G            | 57    | M | 67    | g | 77    | w            |

| 28    | (  | 38    | 8 | 48    | Н            | 58    | X | 68    | h | 78    | х            |

| 29    | )  | 39    | 9 | 49    | Ι            | 59    | Y | 69    | I | 79    | у            |

| 2A    | *  | 3A    | : | 4A    | J            | 5A    | Z | 6A    | j | 7A    | $\mathbf{z}$ |

| 2B    | +  | 3B    | ; | 4B    | K            | 5B    | [ | 6B    | k | 7B    | {            |

| 2C    | ,  | 3C    | < | 4C    | L            | 5C    | \ | 6C    | 1 | 7C    |              |

| 2D    | -  | 3D    | = | 4D    | M            | 5D    | ] | 6D    | m | 7D    | }            |

| 2E    |    | 3E    | > | 4E    | N            | 5E    |   | 6E    | n | 7E    | "            |

| 2F    | /  | 3F    | ? | 4F    | 0            | 5F    | - | 6F    | o | 7F    | DEL          |

#### ГЛАВА 3

#### ПЕРЕКЛЮЧАТЕЛЬНАЯ АЛГЕБРА

Цифровая техника имеет то преимущество перед аналоговой техникой, что она основывается на относительно простой, но при этом мощной теории, на Булевой алгебре, называемой также переключательной алгеброй. В данной главе представлены теоретические основы цифровой техники. Булева алгебра может быть применена для решения почти всех возникающих при разработке цифровых схем проблем при условии выполнения технологических предпосылок, которые рассматриваются в главе 4.

## 3.1. Переключательная переменная и переключательная функция

В цифровой технике применяют специальные переменные и функции. Под Булевой переменной понимают переменную, которая может принимать только значения 0 и 1. С Булевыми переменными могут быть образованы функции. Функцию:

$$y = f(x_1, x_2, x_3, \dots x_n)$$

при  $x_i, y \in \{0, 1\}$  (3.1)

называют n-разрядной переключательной или двоичной функцией. Область значений подобной функции также определяется двоичной системой счисления с элементами 0 и 1. Функции могут быть определены таблицами, в которых величины функций связываются с возможными  $2^n$  комбинациями n входных переменных. Эти таблицы называются таблицами истинности.

Очень простая функция, которая связывает входную переменную x с выходной переменной y, представлена в табл. 3.1. Можно видеть, что все переключательные функции могут быть определены таблицей, в которой содержатся все входные переменные, поскольку учитывать необходимо только два элемента 0 и 1.

Определенную табл. 3.1 переключательную функцию y=f(x) именуют «отрицание», «дополнение» или НЕТ (NOT). В последующем она обозначается оператором «¬» и читается «y равен не x»:

$$y = \neg x. \tag{3.2}$$

Таблица 3.1. Таблица истинности инвертора:

|   | y |

|---|---|

| 0 | 1 |

| 1 | 0 |

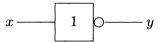

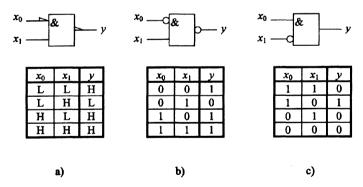

«Отрицание» является одноразрядной переключательной функцией, поскольку она обладает только одним входным символом. Схемный элемент «инвертор» обозначается с помощью схемного обозначения, представленного на рис. 3.1:

Рис. 3.1. Схемное обозначение инвертора.

Имеются ли еще одноразрядные переключательные функции? Путем систематических проб находим их общим числом 4, все они сведены в табл. 3.2. Других видов одноразрядной переключательной функции y не существует. Переключательные функции y=0 и y=1 вырабатывают постоянные, которые не зависят от входа. Поэтому существенной для переключательной алгебры является только одноразрядная двоичная функция  $y=\neg x$ .

Таблица 3.2. Одноразрядные двоичные функции.

| Таблица истинности                                                   | Функции      | Схемное обозначение | Наименование                                        |

|----------------------------------------------------------------------|--------------|---------------------|-----------------------------------------------------|

| $\begin{bmatrix} x & y \\ 0 & 0 \\ 1 & 0 \end{bmatrix}$              | y = 0        |                     |                                                     |

| $\begin{bmatrix} x & y \\ 0 & 0 \\ 1 & 1 \end{bmatrix}$              | y = x        | x1 y                |                                                     |

| $ \begin{array}{c c} x & y \\ 0 & 1 \\ \hline 1 & 0 \\ \end{array} $ | $y = \neg x$ | x—1 $p$ — $y$       | НЕТ,<br>«дополнение»,<br>«отрицание»,<br>«инверсия» |

| $\begin{bmatrix} x & y \\ 0 & 1 \\ 1 & 1 \end{bmatrix}$              | y = 1        |                     |                                                     |

#### 3.2. Двухразрядные переключательные функции.

В принципе можно образовывать произвольные двоичные функции многих входных переменных. Но оказалось практичным вначале рассматривать только функции с одной или двумя входными переменными, а функции с большим количеством входных переменных сводить к ним.

Двоичную функцию с входными переменными  $x_0$  и  $x_1$  также можно определить с помощью таблицы. Комбинацию входных переменных  $x_0$  и  $x_1$ можно представить в виде вектора  $X=[x_0,x_1]$ . Двум входным переменным соответствуют 4 возможных входных вектора X, которые часто индицируются через их десятичные эквиваленты. Так  $x_2$  означает, что  $x_1=1$  и  $x_0=0$ , или, выражаясь по-другому, что  $x_2=[x_0,x_1]=[0,1]$ .

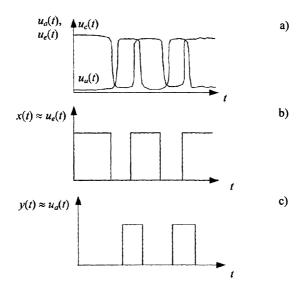

Наряду с «отрицанием» технически возможными являются основные логические элементы И или ИЛИ, которые определяются табл. 3.3. Также обозначают И как AND или «конъюнкция»; ИЛИ как OR или «дизъюнкция».

| Таблица истинности                                      |                                                              |                       |  | Функции              | Схемное обозначение   | Наименование                |

|---------------------------------------------------------|--------------------------------------------------------------|-----------------------|--|----------------------|-----------------------|-----------------------------|

| $\begin{bmatrix} x_1 \\ 0 \\ 0 \\ 1 \\ 1 \end{bmatrix}$ | $egin{array}{c c} x_0 & & & & & & & & & & & & & & & & & & &$ | y<br>0<br>0<br>0<br>1 |  | $y = x_0 \wedge x_1$ | $x_0$ $x_1$ $x_2$ $y$ | И,<br>AND,<br>«конъюнкция»  |

| $\begin{bmatrix} x_1 \\ 0 \\ 0 \\ 1 \\ 1 \end{bmatrix}$ | $egin{array}{ c c c c c c c c c c c c c c c c c c c$         | y<br>0<br>1<br>1<br>0 |  | $y = x_0 \lor x_1$   | $x_0$ $\geq 1$ $y$    | ИЛИ,<br>OR,<br>«дизъюнкция» |

Таблица 3.3. Основные логические элементы И и ИЛИ.

Возникает вопрос о других возможных двухразрядных двоичных функциях. Чтобы системно ответить на этот вопрос, можно осуществить перестановку значений входных переменных y, которые можно получить из четырех возможных входных векторов. В общем случае функция  $y(x_1,x_0)$  может быть определена таблицей истинности (табл. 3.4).

На основе этой таблицы можно сделать заключение о возможности образования  $2^4=16$  различных двоичных функций с двумя

входными переменными. Все возможные двухразрядные двоичные функции приведены в табл. 3.6. Представление двоичных функций выполнено в соответствии со стандартом DIN [43].

Таблица 3.4. Таблица истинности для двухразрядной двоичной функции.

| $x_1$ | $x_0$ | y       |

|-------|-------|---------|

| 0     | 0     | y(0,0)  |

| 0     | 1     | y(0, 1) |

| 1     | 0     | y(1, 0) |

| 1     | 1     | y(1, 1) |

Технически важными функциями NAND, NOR, «эквивалентность» и EXOR (также «исключительное ИЛИ», дизъюнкция) соответствуют собственные логические символы. На практике они часто реализуются на основе специальных схем.

В этой таблице показано, что отдельные функции могут быть представлены только с помощью логических элементов AND, OR и NOT. Поэтому каждая логическая функция может быть представлена с помощью этих трех логических элементов. Все двоичные функции также могут быть представлены с помощью функции NOR, точно также и с помощью NAND. Поэтому эти функции называют совершенными.

Доказательство эквивалентности можно привести путем размещения таблиц истинности. Таким образом, например, может быть доказана эквивалентность для логического элемента EXOR на основе AND, OR или NOT:

$$x_0 \leftrightarrow x_1 = (\neg x_0 \land x_1) \lor (x_0 \land \neg x_1) \tag{3.3}$$

В табл. 3.5 вначале оцениваются оба выражения в скобках. Затем формируется логическое OR, соответствующее обоим выражениям в скобках, и вписывается в пустую колонку. Так как последняя и предпоследняя колонки совпадают, уравнение доказано, поскольку в последней колонке стоит определение функции «исключительное ИЛИ» (то есть EXOR).

Таблица 3.5. Доказательство на основе таблицы истинности.

| $x_1$ | $x_0$ | $\neg x_0 \wedge x_1$ | $x_0 \wedge \neg x_1$ | $(\neg x_0 \land x_1) \lor (x_0 \land \neg x_1)$ | $x_0 \leftrightarrow x_1$ |

|-------|-------|-----------------------|-----------------------|--------------------------------------------------|---------------------------|

| 0     | 0     | 0                     | 0                     | 0                                                | 0                         |

| 0     | 1     | 0                     | 1                     | 1                                                | 1                         |

| 1     | 0     | 1                     | 0                     | 1                                                | 1                         |

| 1     | 0     | 0                     | 0                     | 0                                                | 1                         |

**Таблица 3.6.** Двухразрядные двоичные функции: таблица истинности, представление на основе (AND, NOT, OR), логический символ и название функции.

| Таблица<br>истинности                                                       | Функции                                                                                   | Схемное<br>обозначение                          | Наименование    |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------|

| $egin{array}{ c c c c c c c c c c c c c c c c c c c$                        |                                                                                           |                                                 |                 |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                      | y = 0                                                                                     |                                                 | нуль            |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                      | $y = \neg (x_0 \lor x_1)$ $y = (x_0 \overline{\lor} x_1)$                                 | $x_0$ $\ge 1$ $\longrightarrow y$               | NOR             |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                      | $y = x_0 \land \neg x_1$                                                                  |                                                 | запрет          |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                      | $y = \neg x_1$                                                                            |                                                 | дополнение      |

| $\begin{array}{ c c c c c c }\hline y & 0 & 1 & 0 & 0\\\hline \end{array}$  | $y = \neg x_0 \wedge x_1$                                                                 |                                                 | запрет          |

| $\begin{array}{ c c c c c c }\hline y & 0 & 1 & 0 & 1\\\hline \end{array}$  | $y = \neg x_0$                                                                            |                                                 | дополнение      |

| y 0 1 1 0                                                                   | $y = (\neg x_0 \land x_1) \lor  \lor (x_0 \land \neq x_1)  y = (x_0 \Leftrightarrow x_1)$ | $x_0$ =1 $y$                                    | EXOR            |

| y 0 1 1 1                                                                   | $y = \neg (x_0 \land x_1)$ $y = (x_0 \bar{\land} x_1)$                                    | $x_0$ & $y$                                     | NAND            |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                      | $y = x_0 \wedge x_1$                                                                      | $\begin{bmatrix} x_0 & \\ x_1 & \end{bmatrix} $ | AND             |

| y 1 0 0 1                                                                   | $y = (x_0 \land x_1) \lor  \lor (\neg x_0 \land x_1)  y = (x_0 \leftrightarrow x_1)$      | $x_0$ = $y$                                     | эквивалентность |

| $\begin{array}{ c c c c c c }\hline y & 1 & 0 & 1 & 0 \\\hline \end{array}$ | $y = x_0$                                                                                 |                                                 | идентичность    |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                      | $y = x_0 \lor \neg x_1$                                                                   |                                                 | импликация      |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                      | $y=x_1$                                                                                   |                                                 | идентичность    |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                      | $y = x_1 \lor \neg x_0$                                                                   |                                                 | импликация      |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                      | $y = x_0 \lor x_1$                                                                        | $x_0$ $\geq 1$ $y$                              | OR              |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                      | y = 1                                                                                     |                                                 | единица         |

# 3.3. Вычислительные правила

Важными для упрощения сложных функций являются вычислительные правила булевой алгебры. Для доказательства отдельных законов могут быть использованы таблицы истинности.

Вычислительные правила булевой алгебры перечислены ниже. Переместительный (коммутативный) закон:

$$x_0 \wedge x_1 = x_1 \wedge x_0 \tag{3.4}$$

$$x_0 \lor x_1 = x_1 \lor x_0 \tag{3.5}$$

Сочетательный (ассоциативный) закон:

$$(x_0 \land x_1) \land x_2 = x_0 \land (x_1 \land x_2) \tag{3.6}$$

$$(x_0 \lor x_1) \lor x_2 = x_0 \lor (x_1 \lor x_2) \tag{3.7}$$

Распределительный закон (закон дистрибутивности):

$$x_0 \wedge (x_1 \vee x_2) = (x_0 \wedge x_1) \vee (x_0 \wedge x_2) \tag{3.8}$$

$$x_0 \lor (x_1 \land x_2) = (x_0 \lor x_1) \land (x_0 \lor x_2) \tag{3.9}$$

Закон поглощения (закон абсорбции):

$$x_0 \land (x_0 \lor x_1) = x_0 \tag{3.10}$$

$$x_0 \lor (x_0 \land x_1) = x_0 \tag{3.11}$$

Существование нейтральных элементов:

$$x_0 \wedge 1 = x_0 \tag{3.12}$$

$$x_0 \lor 0 = x_0 \tag{3.13}$$

Существование дополнительных элементов:

$$x_0 \land \neg x_0 = 0 \tag{3.14}$$

$$x_0 \lor \neg x_0 = 1 \tag{3.15}$$

Теорема Де-Моргана:

$$x_0 \wedge x_1 = \neg \left(\neg x_0 \vee \neg x_1\right) \tag{3.16}$$

$$x_0 \lor x_1 = \neg (\neg x_0 \land \neg x_1) \tag{3.17}$$

На основе симметрии законов можно сделать следующие выводы. Если справедлив один закон, то справедлив и закон, который получают путем взаимной замены AND и OR и постоянных 0 и 1. Полученный таким образом закон называют дуальным законом. Как, например, законы (3.16) и (3.17) дуальны по отношению друг к другу. Аналогично обозначают функцию F', которая получилась из

функции F путем замены AND на OR и 0 на 1, как функцию, дуальную по отношению к F.

Важно также установить, что NAND и NOR не являются ассоциативными. И так, справедливо:

$$(x_0\bar{\wedge}x_1)\bar{\wedge}x_2 \neq x_0\bar{\wedge}(x_1\bar{\wedge}x_2) \tag{3.18}$$

$$(x_0 \overline{\vee} x_1) \overline{\vee} x_2 \neq x_0 \overline{\vee} (x_1 \overline{\vee} x_2) \tag{3.19}$$

# 3.4. Каноническая дизъюнктивная нормальная форма (KDNF).

Любую двоичную функцию можно представить с использованием только логических элементов AND, OR или NOT. Это может быть выполнено на основе систематического подхода, как в примере с функциями, приведенными в табл. 3.7. Можно действовать двумя различными способами. Мы начнем с канонической нормальной дизъюнктивной формы (KDNF).

| $x_2$ | $x_1$ | $x_0$ | Десятичный | y |

|-------|-------|-------|------------|---|

| 0     | 0     | 0     | 0          | 1 |

| 0     | 0     | 1     | 1          | 0 |

| 0     | 1     | 0     | 2          | 1 |

**Таблица 3.7.** Таблица истинности для примера с KDNF.

Для этого рассмотрим сначала входные векторы  $x_i$ , для которых функция y = f(x) принимает значение 1. Следовательно, для этих входных векторов справедливо  $f(x_i) = 1$ . В нашем случае это  $x_0$ ,  $x_2$ ,  $x_3$ ,  $x_5$  и  $x_6$ . Проведем для каждого подобного входного вектора операцию конъюнкции (логического умножения, И) с элементом  $x_i$ , который как раз для этого входного вектора принимает значение 1. Для  $x_5$  было бы:

$$m_5 = x_2 \land \neg x_1 \land x_0 \tag{3.20}$$

$m_5$  называют также «минтермом». Минтермы содержат всегда все входные переменные, поэтому их называют полной конъюнкцией.

В случае минтерма, входные переменные могут быть инвертированными либо не инвертированными, в зависимости от того, что представляет собой переменная 1 или 0. В этом примере входные минтермы имеют вид:

$$m_0 = \neg x_2 \land \neg x_1 \land \neg x_0 \tag{3.21}$$

$$m_2 = \neg x_2 \land x_1 \land \neg x_0 \tag{3.22}$$

$$m_3 = \neg \, x_2 \land x_1 \land x_0 \tag{3.23}$$

$$m_6 = x_2 \wedge x_1 \wedge \neg x_0 \tag{3.24}$$

Следовательно, при определенном варианте входных переменных минтерм имеет значение 1.

Вся функция может быть представлена на основе дизъюнкции (логическое сложение) минтермов. Функция получает значение 1, когда, по крайней мере, один из минтермов равен 1. Этот способ представления называется «канонической дизъюнктивной нормальной формой» (KDNF). В нашем случае функция может быть представлена следующим образом:

$$y = (\neg x_2 \land \neg x_1 \land \neg x_0) \lor (\neg x_2 \land x_1 \land \neg x_0) \lor \lor (\neg x_2 \land x_1 \land x_0) \lor (x_2 \land \neg x_1 \land x_0) \lor (x_2 \land x_1 \land \neg x_0)$$

$$(3.25)$$

# 3.5. Каноническая конъюнктивная нормальная форма (KKNF)

В качестве альтернативы для представления функции могут быть применены входные векторы  $x_i$ , при которых функция принимает значение 0, то есть когда будет справедливо равенство  $f(x_i)=0$ . Для функции показанной в табл. 3.7, такими векторами будут  $x_1, x_4$  и  $x_7$ .

Сформируем так называемые макстермы. Это дизъюнкции, которые равны 0, когда приложен соответствующий входной вектор  $x_i$ :

$$M_1 = x_2 \lor x_1 \lor \neg x_0 \tag{3.26}$$

$$M_4 = \neg x_2 \lor x_1 \lor x_0 \tag{3.27}$$

$$M_7 = \neg x_2 \lor \neg x_1 \lor \neg x_0 \tag{3.28}$$

Итак, входные переменные, которые в входом векторе равны 1, выступают в макстерме инвертировано. Входные переменные, которые в входном векторе равны 0, появляются в макстерме в неинвертированном виде. Таким образом, макстерм равен 0 только для  $x_2=0,\,x_1=0$  и  $x_0=0.$

Вся функция может быть представлена теперь на основе конъюнкции макстермов, так как значение функции только тогда равно 0, когда, по крайней мере, один из макстермов равен 0. Форма представления, называемая как «каноническая конъюнктивная нормальная форма» (ККNF), представлена в следующем примере:

$$y = (x_2 \lor x_1 \lor \neg x_0) \land (\neg x_2 \lor x_1 \lor x_0) \land (\neg x_2 \lor \neg x_1 \lor \neg x_0) \quad (3.29)$$

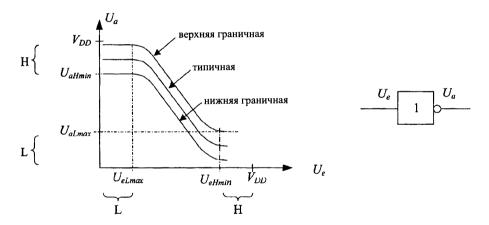

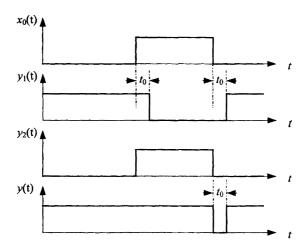

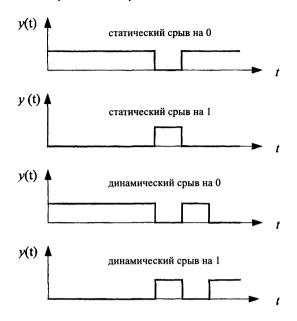

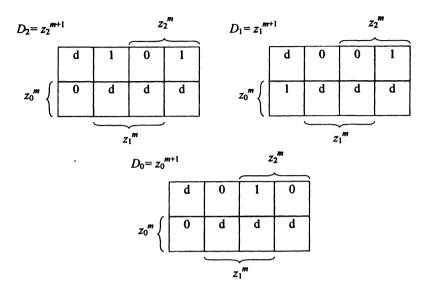

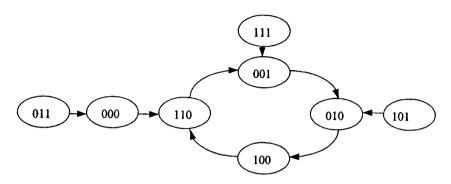

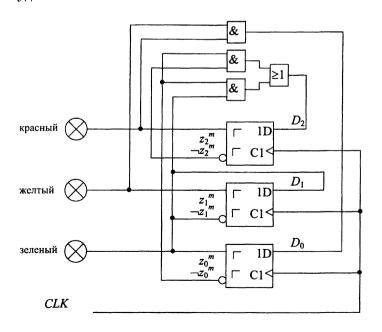

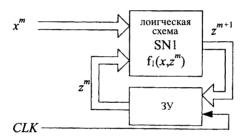

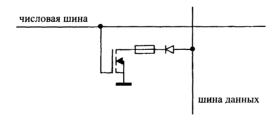

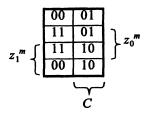

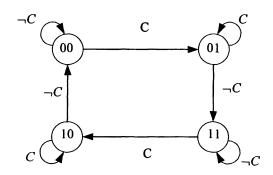

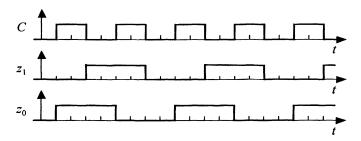

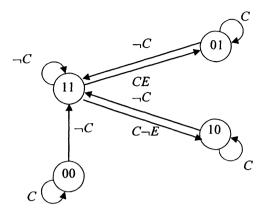

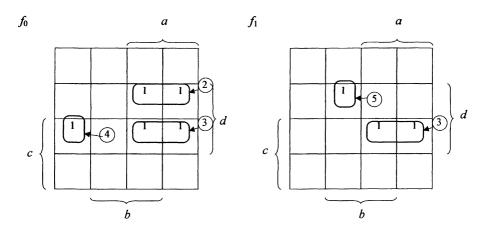

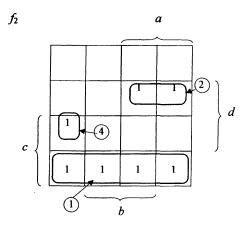

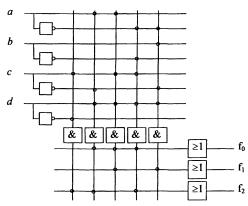

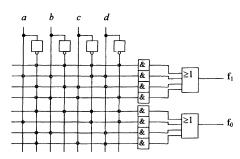

# 3.6. Представление функций с помощью KKNF и KDNF.